フォーラムへの返信

-

投稿者投稿

-

maida様

お問い合わせ頂きましてありがとう御座います。

電流制限はRextにて設定され、全CH共通で反映されるため、CH毎に設定することはできません。

CH毎に輝度(電流値)を設定する場合にはAddress_0x02~0x11にてDutyを調整して頂きたく存じます。ご参考になれば幸で御座います。

Polnarefwdwune様

>> 磁気飽和時とは、インダクタンスの磁気飽和により電流が制限されずに跳ね上がり

>> ショート保護動作に引っかかるという認識であっていますでしょうか?

御認識の通りで御座います。>> どういうつながりがあると考えられますでしょうか?

相対的にクロスオーバー周波数が低下したためと思われます。しかしながら根本的な解決策とは言えないため、

LとCoutを大きくし、fswを下げる等、恒久的な対策が必要かと思われます。Polnaref

wdwune様

御問合せ頂きましてありがとうございます。

>> 電圧最大値は 8.0Vになっているのですが、問題ないのでしょうか?

8Vを超える電圧が100nsec未満であれば問題御座いません。

※100nsec:内蔵保護ダイオードのTrr(max)>> ノイズにより、-電位も観測されています。 こちらは問題ありますでしょうか?

>> また、この際の定格はありますでしょうか?

絶対最大定格では-0.4Vと規定されて御座います。

こちらも問題御座いません。ご参考になれば幸で御座います。

PolnarefUMA様

御問合せ頂きましてありがとう御座います。

>> 未実装、もしくはコンデンサをつけておいた方が良いのか、アドバイスを頂けませんでしょうか?

設計上の判断になりますので0_or_1で回答することが難しいですが、私の個人的な意見としては、

「とりあえず実装できるようにしておく」が良いと思います。>> 実装したほうが良いとした場合、どの程度の容量を接続すれば良いでしょうか?

動作に影響を及ぼす周波数に依存するため、一概にお答えいたしかねます。

セミラックコンデンサはサイズと容量により、インピーダンスが最小となる周波数が異なります。

実機動作において、fswがノイズの影響によりバタつく場合に、症状の度合いを見ながら

容量を調整するしかないと考えます。>> 容量が適正ではない場合、どのような動作が現れると考えられますか?

コンデンサは一般的に周波数が高くなるとインピーダンスが低下していきますが、ESLがあるため、

ある周波数を境にインピーダンスは増加していきます。

インピーダンスの増加はノイズに対しGain(増幅度)として作用するため、ノイズの強度がfswの

安定性に影響を及ぼすことが考えられます。ご参考になれば幸で御座います。

Polnaref

wdwune様

>> ショート保護においてブランクアウト時間を無視できるということでしょうか?

はい、出力短絡又は磁気飽和時には問答無用で停止致します。>> 右半面のゼロというのはどういうことでしょうか?

RHPZ(right half plane zero)で検索しますと多くの文献がHitします。

昇圧比が大きい(Vin低⇒Vout高orPout大)の時に制御が破綻する現象です。昇圧DC/DCでのみ現れます。

詳しくは下記URLを御参照ください。

http://www.ti.com/jp/lit/ds/symlink/lm2700.pdf

http://www.tij.co.jp/jp/lit/an/jaja461/jaja461.pdfPolnaref

-

この返信は6 年、 1 ヶ月前に

短絡亭過電流 さんが編集しました。理由: URL削除

wdwune様

データシート「7.3.4 Short-Circuit Protection」に

====

When the voltage across the sense resistor measured on the I SEN pin exceeds 343 mV, short circuit current limit protection gets activated.

A comparator inside the LM3478 reduces the switching frequency by a factor of 5 and maintains this condition until the short is removed.

In normal operation the sensed current will trigger the power MOSFET to turn off.

During the blanking interval the PWM comparator will not react to an over current so that this additional 343 mV current limit threshold is implemented to protect the device in a short circuit or severe overload condition.

====

と記載されております通り、Isenピンの電圧が343mVになった際に、強制的に「過電流」と判定いたします。>> 原因は何だと考えられるでしょうか?

右半平面のゼロかもしれません。

LとCoutを大きくし、fswを下げることで上記症状が緩和した場合、その可能性が大きいと思われます。Polnaref

wdwune様

データシートp11、Fig20に記載されております様に、FETターンオンから325nsec間は、電流検出抵抗の電圧は無視されます。

ターンオン直後のサージは珍しいものではなく、その対策の為です。>> 間違っていた場合、最小ON時間とブランクアウト時間はは形状でも一致するはずでしょうか?

最小ON時間とブランクアウト時間はイコールとなります。ご参考になれば幸で御座います。

Polnaref

wdwune様

申し訳ありません。「容量」を「Cin」と勘違いしておりました。

>> 容量が低い場合添付波形のように、FETの起動時、停止時にIsen端子電圧が急峻な変動を起こします。

FETのDrainから流入する電流波形と、電流検出抵抗で観測される電流波形は、寄生容量及び寄生インダクタンスにより、完全に一致することは御座いません。コンデンサの増設によりそれら寄生成分が吸収されたものと思われます。>> つまり、Isen端子容量を大きくしたことで、安定的な動作となったということでしょうか?

その御理解で結構です。

Lを上げることでも同様の結果となります。>> Isen端子電圧に急峻な変化が起こらなくなります。

>> この改善は、動作の安定性によるものなのでしょうか?

寄生容量からの放電や寄生インダクタンスによるサージ成分を増設したコンデンサが吸収したためと思われます。ご参考になれば幸で御座います。

Polnaref

wdwune様

>> 電流検出のスロープに対し余裕ができたというのはどういうことでしょうか?

データシートp14に以下の記述が御座います。「For more flexibility, slope compensation can be increased by adding one external resistor, R SL , in the I SEN ‘s path. Figure 23 shows the setup. The externally generated slope compensation is then added to the internal slope compensation of the LM3478. When using external slope compensation, the formula for S e becomes:

It is a good design practice to only add as much slope compensation as needed to avoid sub-harmonic oscillation. Additional slope compensation minimizes the influence of the sensed current in the control loop. With very large slope compensation the control loop characteristics are similar to a voltage mode regulator which compares the error voltage to a saw tooth waveform rather than the inductor current.」

LM3478はリリースが2000年と古く、応答速度はそれほど早くありません。そのため、スイッチング毎に急峻な電流の変化があった場合、帰還系において追従できず、正常な動作ができなくなる可能性が御座います。そのため実際の電流波形よりやや緩慢な電流波形に加工することで、安定的な動作にすることができます。

副作用と致しましては、応答性が悪くなるため、出力電流の急峻な変化が発生した場合、出力電圧が振られ、収束するまで時間を要します。過電流発生からTripまでの時間が伸びます。

>> 容量が低い場合添付波形のように、FETの起動時、停止時にIsen端子電圧が急峻な変動を起こします。

Vinそのものが低下しているのではないでしょうか?

御確認頂きたく存じます。ご参考になれば幸で御座います。

Polnaref

wdwune様

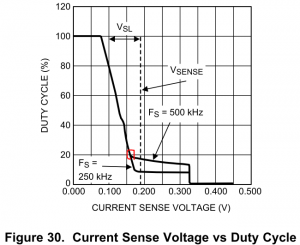

>> ちなみに、 156mVというのは デューティー変動の変化が小さくなる領域になる際の

>> Isen 端子電圧という認識であっているのでしょうか?

fsw=400kHzにおいて、DutyとVsenseが線形な特性示す領域の、Vsenseの最大値です。

添付図赤丸部分とお考え下さい。>> 立ち下がりの際に発生しているノイズの原因は何だと考えられるでしょうか?

FETには寄生容量(Ciss,Coss,Crss)があり、Ciss,Coss,はFET_ON時にD→S方向へ放電されます。

放電された電流を電流検出抵抗が拾ってしまっているものと思われます。Polnaref

Attachments:

wdwune様

電流スロープ補償が足りていないものと思われます。

>> Isen端子の容量 Csn=0.01uF 大きくすると改善がみられる状況です。

Cを追加することで電流検出の経路にLPFが構成され、電流検出のスロープに対し余裕ができたものと考えます。

応答は遅くなりますが、帰還系としましては安定方向に向かったものと思われます。

確認手段としてはボード線図の測定が有効と存じます。>> Csnの容量0.047uFを使用しようと思っているのですが、問題はありませんでしょうか?

ICと致しましては、問題御座いません。ご参考になれば幸で御座います。

Polnaref

wdwune様

お問い合わせ頂きましてありがとう御座います。

御推察の通り過電流が働いているものと思われます。>> しかし、Vsen閾値はtyp.156mV に対し添付波形は、ノイズのみ閾値を超え、

>> リニア的に増加している部分に関しては100mV程度となっています。

過電流の閾値は固定ではなくDutyにより変化致します。

データシートp20「8.2.1.2.4 Setting the Current Limit」を御参照頂きたく存じます。ご参考になれば幸で御座います。

Polnaref

-

この返信は6 年、 1 ヶ月前に

短絡亭過電流 さんが編集しました。

aikawa様

御問合せ頂きましてありがとう御座います。

5usというのは10%⇔90%での時間でしょうか?

入力が出力に反映されるまでの遅延時間をPropagation delay time(伝搬遅延時間)と表記いたします。

Propagation delay timeは電源電圧に依存しており、電源電圧が高いほど遅延は小さくなります。

詳細についてはデータシートのp8~p10を御参照ください。ご参考になれば幸で御座います。

Polnaref

-

この返信は6 年、 1 ヶ月前に

短絡亭過電流 さんが編集しました。

wdwune様

お問い合わせ頂きましてありがとう御座います。

直感的には

A) Vinの供給源の出力インピーダンスが大きく、スイッチング毎にVinが振られる

B) Qgの大きなFETを使用しており、Vin低下時にはCinの電荷が十分になく、スイッチング毎にVinが振られる

C) Vin低下時にはDutyが広がり、50%を超えるため、電流モード特有のサブハーモニック現象が起きている

の3つが考えられます。A,Bは凡そ似た内容であり、Cinを増設することで緩和することができます。

Cは電流モードという制御系固有の現象であり、Dutyが広がり過ぎないよう、作り込む必要が御座います。。

サブハーモニックに関しましてはデータシートp13、「7.3.2 Slope Compensation Ramp」を御参照ください。ご参考になれば幸で御座います。

Polnaref

wdwune様

>> 動作電流を引けなくなる以外にどのような問題が起こるのでしょうか?

ICとしましては、データシート記載のVcc(min)を割り込まなければ正常に動作致します。

考えられるのは、設計後の実動作上において、放射ノイズの懸念が考えられます。FETをONする際のGate電圧がVccの変動に依存するため、電圧によってFETのTurn-ON/OFF時間が変化致します。

PWBのパターンが適切であれば”ある程度は”抑えられますが、さらなる対策が必要となりますと、FETのGate抵抗の調整が必要になると思われます。

Gateの抵抗を大きくしますと、放射のレベルは低減しますが、その分FETでのスイッチ損が増加し、その分放熱を要する場合が御座います。つまり、Vccが変動する環境下では、放射ノイズに対する対策の「最適点」を見つけることが難しくなります。

従いまして、今回のケースでは、もし可能ならばVccの固定(Max6.5V程度でクランプ)が望ましく思います。

Polnaref

-

この返信は6 年、 1 ヶ月前に

-

投稿者投稿