フォーラムへの返信

-

投稿者投稿

-

KATANA様

ご投稿いただきありがとうございます。

以下回答差し上げます。

>1. USBコンプライアンステストの際、テストモードへの移行方法を教えてください(Upstream・Downstream)

USB.orgより提供されてい XHCI HSETT toolsを使用する事によって、TEST modeへの移行が可能です。

>2. OTP設定方法を教えてください

>3. OTPでUSB2.0ポートのポラリティをスワップする際、設定前からスワップするポートが接続状態で問題はないでしょうか?

個別にてご連絡さしあげます。

以上、よろしくお願い致します。

QT

HIGA様

ご投稿いただきありがとうございます。

-側電源範囲につきまして、絶対値としての制約はなく、あくまで+側電源との相対的な規定となります。

Recommended Operating Conditionとして(V+)-(V-)=36Vとなりますので、

+電源が15Vの場合、-電源の最低推奨値は-21Vとなります。

また危惧される事として、一般的に入出力信号が電源レール付近になると特性が悪化する傾向がございます。

詳細はデータシートをご参照いただければと思いますが、

可能な限り入出力信号レベルに対して余裕を持った電源電圧に設定される事が理想的です。

以上、何卒よろしくお願い致します。

QT

-

この返信は7 年、 2 ヶ月前に

QT さんが編集しました。

QT さんが編集しました。

Osugi様

>了解しました、電源端子±VSがOFF(0V)の時のデータは無いと思いますが、

>同じようなグラフとなるという理解で良いでしょうか。Vs=±0Vだとアンプが動作していない状態ですので定量的に同じかどうかは申し上げづらいですが、

ダイオード経由で電流が流れる傾向は同じものと考えます。

なお、Vs=±0Vであれば内部のトランジスタが動作しませんので、出力電圧は出せないものと考えます。

なおREF端子について確認した所、こちらは電源電圧以上の電圧が印加されるとダメージを負う可能性あるとの事です。

以上、よろしくお願い致します。

QT

Osugi様

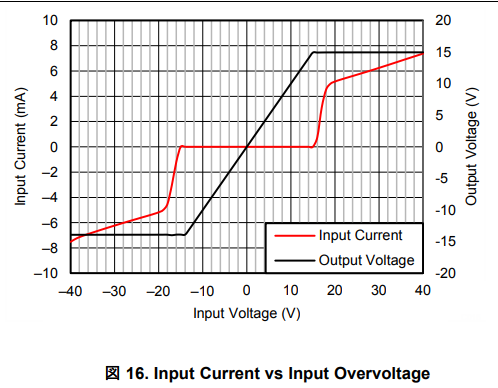

データシートを抜粋してしまったので詳細が記載されておりませんが、

こちらは±Vs=15V時の特性になります。

グラフを見ると±Vs=15V付近で特性に変化が見られますので、入力端子特性はVsに依存すると考えられます。

この特性が許容できるかどうか、ご判断いただければと思います。

以上、何卒よろしくお願い致します。

QT

-

この返信は7 年、 3 ヶ月前に

QT さんが編集しました。

QT さんが編集しました。

Osugi様

ご投稿いただきありがとうございます。

入力端子の対入力電圧特性についてはデータシート記載の下図をご参考ください。

REF端子についてはTIに確認中ですので、もう少々お時間いただければと思います。

QT

Osugi様

②④につきまして、以下回答差し上げます。①については、ご確認をお願いいたします。

①内部レジスタの耐久回数について

想定として、どの程度の期間にどの程度の頻度で変換が行われる可能性があるか、ご教示いただけますでしょうか?

その情報をベースにTIに確認させていただければと思います。

②AGND1とAGND2について

データシートP6に記載されている様に、AGND1は内部リファレンスGNDとなるためきれいな(電流が流れない)ノードと接続する必要がございます。一方AGND2は、データシートFigure32でCAP端子容量のGNDと接続されている事からも、AGND1程はシビアでないものと推測されます。

④アナログ入力段の外部コンデンサについて

ADC入力に接続される容量は、ADC内部のS/H容量を充電する際に電荷の供給を補足ために配置されるものですので、”確実に”必要という訳ではないと考えます。

ただ、入力容量を配置する事でアンプのコスト(≒帯域)を抑えつつ、S/H容量の充電を間に合わせる手法が取られる事は一般的と考えますので、

試作の際には少なくともコンデンサ(と抵抗)のパターンを準備しておいた方がよろしいかと思います。

以上、ご確認の程よろしくお願い致します。

QT

HIGA様

お時間を要し申し訳ございませんでした。

残念ながらTIはご所望のデータを所持していないとの事です。

ご期待に添えず申し訳ありませんが、何卒よろしくお願い致します。

QT

Osugi様

ご投稿いただきありがとうございます。

取り急ぎ③⑤について回答させていただきます。

③TAG入力端子について

データシートFigure 2の左下にTAGがLowに接続されている旨記載がございますので、

Lowで問題ないと考えます。

⑤データ取り出しのシリアル通信について

データシートP6のDATAの欄に”. If EXT/INT is low, data are valid on both the rising and falling edges of DATACLK”と記載がございますので、立ち上がり/下りの両エッジで出力されると考えます。

①②④については確認出来次第回答差し上げます。

以上、何卒よろしくお願い致します。

QT

-

この返信は7 年、 3 ヶ月前に

QT さんが編集しました。

QT さんが編集しました。

HIGA様

ご投稿いただきありがとうございます。

ご質問の件現在TIに確認しておりますが、米国が連休中であり返信が遅くなっている状況です。

ご不便おかけし恐縮ですが、もうしばらくお時間いただければと思います。

以上、何卒よろしくお願い致します。

QT

OZSHG1231様

ご投稿いただきありがとうございます。

ご質問の件ですが、まずADS42JB69EVMと組になるのは、下記資料の通りTSW14J56になります。

http://www.tij.co.jp/tool/jp/ADS42JB69EVM

TSW14J56を使用することでデータの取得がPCで可能になります。

アナログ信号生成機能はTSW14J56にはないと考えます。

また、恐縮ながらADS42JB69EVMにTSW14J56は同梱されていないため、

それぞれご購入いただく必要がございます。

以上、何卒よろしくお願い致します。

QT

-

この返信は7 年、 3 ヶ月前に

QT さんが編集しました。

QT さんが編集しました。

madridista様

ご投稿いただきありがとうございます。

ご質問の件ですが、TYP値と異なりMAX値は保証値となりますので、そちらの提示はご容赦いただければと思います。

しかしながら、±20ppm/℃は±1σの値となりますので、±3σとなる±60ppm/℃が現実的な実力値となります(あくまで保証値ではなく参考値となります)。

以上、ご参考の程よろしくお願い致します。

QT

Osugi様

ご投稿いただきありがとうございます。

ご質問の件についてですが、

“External clock (can run continually but not recommended for optimum performance)”

はデータシートFigure 8, 9に示されている様に常時CLKが入力される様な状況を指しております。

(Figure3~7ではCLKが不連続になっているのがわかるかと思います)

性能についてですが、データシートP16に”Specifications with a continuously running external clock

cannot be ensured.”と記載がございますので、「とりあえず動作させすればいい」という状況でない限り、常時クロックを入力する事は避けた方がよろしいかと思います。

以上、よろしくお願い致します。

QT

madridista様

ご投稿いただきありがとうございます。

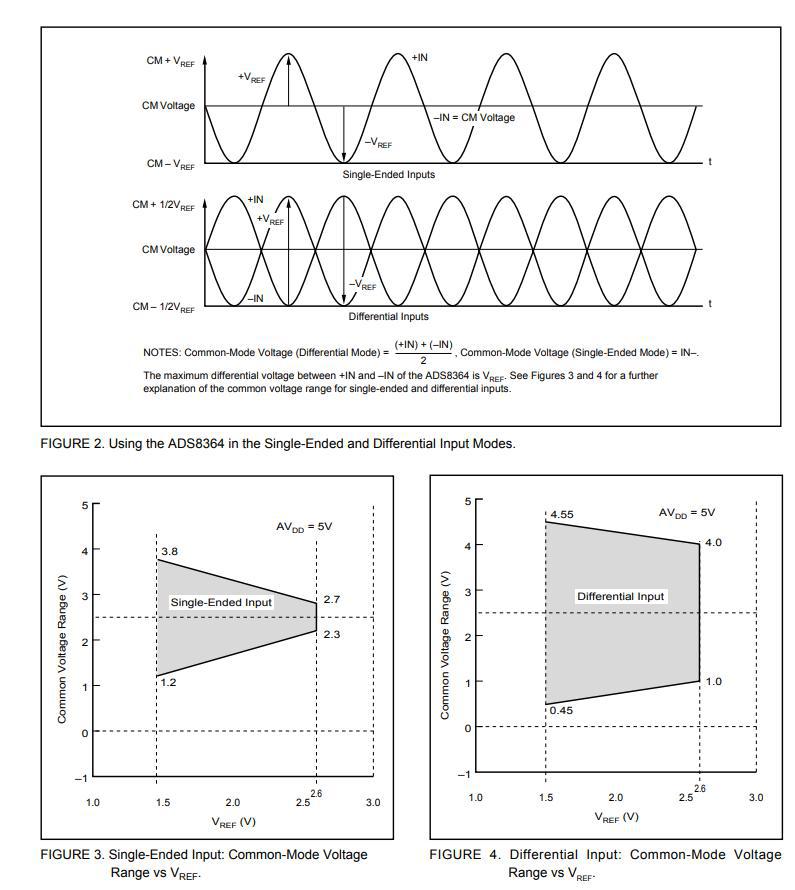

差動入力電圧がVREFを越えている場合、出力のデータはフルスケール値である0b1111111111111111となります。

ご確認の程よろしくお願い致します。

QT

HIGA 様

ご投稿いただきありがとうございます。

内部リファレンスは2.5V固定となりますので、変更はできません。

2.5V以外が必要な場合は外部より電圧を供給する必要がございます。

入力レンジについてはデータシート内のFigure 2~4(下図)をご参照いただければと思います。

以上、よろしくお願いします。

QT

2035様

ご回答ありがとうございます。

結論としては、RESET解除前であれば問題ございません。

Analog to Digital supplyは通常動作時の規定ですのでRESET解除前の状態では適用されません。

以上、何卒よろしくお願い致します。

QT

-

この返信は7 年、 2 ヶ月前に

-

投稿者投稿