フォーラムへの返信

-

投稿者投稿

-

Cruijff様

ご返信ありがとうございます。

>現在発生している症状はリセットICを接続されず、添付いただいた回路通りでしょうか。

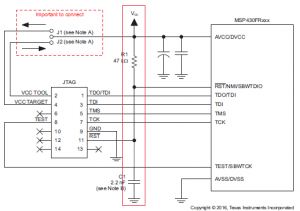

リセットICは取り外しており、コンデンサは実装済みなので推奨回路のように抵抗47kを後付けしております。

なお、回路を確認したところ、所定のコンデンサは1nFが実装されていました。>1. CCSのバージョンはいくつを使用しておりましたでしょうか。

CCSは使用しておらず、EW430を使用しております。ちなみにversionは6.40.1です。念のため確認ですが、

リセット端子部分をJTAGモードで使用する場合の推奨回路にすると、

ツール接続では動くがツールを外すと動作しなくなる(JTAGモード以外で使用する場合は推奨回路が別にある)

ということでしょうか。(違うとは思うのですが。)Ge様

ご返信ありがとうございます。ご指摘の内容で、とりあえずリセット要因がわかりました。

ちなみに、リセット直後のSYSRSTIVを確認したところ、

0020 ということで PMMPW PMM password violation (PUC)が要因とのことでした。

ただ、なぜEINT処理を有効にするとこのPUCがかかってしまうかについては追って確認したいと思います。Cruijff様

ご返信ありがとうございます。>1. ツールを外しての電源供給はDVCC何Vでしょうか。

3.3Vです。値は設計値通りとなります。

>2. 安定化電源による電源供給でも、こちらの現象は発生しますでしょうか。

はい。電源印加後、リセット端子を強制的にVSSに落とし、DVCCに戻すとプログラムが動きだすようです。

ツールにつなぐために、リセット端子部の外付け回路をデータシート記載の添付ファイル赤枠のように追工しているのですが、これがなにか影響しているのでしょうか。(元々、リセットICを接続予定です。)Attachments:

Cruijff様

ご返信ありがとうございます。>fsystem (with FRAM wait state)の通り、NWAITSx = 1と設定する必要がございます。

上記はサンプルプログラムを参照し、既に記載済みです。>3. LPMは使用されておりますでしょうか。使用されている場合、その種類をお教えください。

LPMは使用していません。

>4. I2Cのプルアップ抵抗は外付けで用意されておりますでしょうか。

4pin/5pin ともに1kΩのプルアップ抵抗を接続しています。

(51kΩだとツール接続状態でもI2Cが動かなかったので1kΩに変更しています。

datasheetで探しきれなかったのですが、推奨抵抗値がありましたらご教示願います。)>1. ツールを外しての電源供給はDVCC何Vでしょうか。

>2. 安定化電源による電源供給でも、こちらの現象は発生しますでしょうか。

確認中です。 -

投稿者投稿