フォーラムへの返信

-

投稿者投稿

-

ご投稿ありがとうございます。

C2000-GANGでの書き込み時、「Err 27」が発生するのですが、

これはどういうエラーが教えていただけないでしょうか。弊社で確認した限り、明確な「Err 27」に関する情報が確認出来ませんでした。なお、デバイスは異なりますが、以下のURL情報が関連している可能性がございますので、内容をご確認の上、対策を実施頂けますでしょうか。

- What behaviour happen these MSP-GANG error?

→ターゲットデバイスとC2000-GANG間の接続の確認 - C2000-GANG: C2000-Gang error

→使用しているファームウェアのアップデート

また、お手数ですが、下記の項目についてご教示頂けますでしょうか。

- 使用しているPC:例)Windows10等

- 書き込み対象の型番:

- C2000-GANGの設定と各種バージョン情報:

※下図のように設定とバージョン情報を共有頂ければと存じますが、非表示を希望される部分については、黒く塗り潰す等、見えない形で投稿頂いても問題ございません。 - エラーが表示されている画面のスクリーンショットや写真、ログ情報等:

※エラー番号以外に表示されている情報を共有頂ければと存じます。 - 「Err 27」が発生した際の”Results”の状態:

※VerifyやProgramなどのどのステップまで進んでいるか、共有頂ければと存じます。

以上、よろしくお願いいたします。

ご投稿ありがとうございます。

頂いたご質問につきましては、こちらの投稿のご質問内容と合わせて、現在メーカーに確認させていただいておりますので、大変恐縮ですが、少々お時間頂けますと幸いです。

以上、よろしくお願いいたします。

ご投稿ありがとうございます。

頂いたご質問につきましては、現在メーカーに確認させていただいておりますので、大変恐縮ですが、少々お時間頂けますと幸いです。

なお、現在確認されている問題はTI社より提供されている評価ボード(EVM)でも同様の結果となりますでしょうか。

以上、よろしくお願いいたします。

ご投稿ありがとうございます。

ご質問に関しましては、直接メールにてご連絡させて頂きましたので、別途ご確認いただければと存じます。

つきましては、本スレッドを閉じさせていただきたく宜しくお願い申し上げます。

本件、ご返信が遅くなり大変申し訳ございません。

MSP430FR5859、コンパイラーTI v15.12.3.LTSを使っています。

同じプロジェクトをCCS6.2とCCS12で開くと、StackUsageで確認する数字が一致しない現象があります。

CCS12:mainProcessのInclusiveSizeは120

CCS6.2: mainProcessのInclusiveSizeは1532

原因は何でしょうか。

上記についてメーカーに確認した結果、古いCCSのバージョンでは、Stack Usageの表示にいくつかのバグがあったとのことですので、CCSv12を参照頂ければと存じます。

もしCCS12の内容が適切であれば、mainProcessのInclusiveSizeは120、今のスタック設定256に超えていないのに、なぜ黄色い表示でしょうか?

上記についてメーカーに確認した結果、今回の様な黄色の表示結果となる主な理由の一つは、リンカーに渡されるスタック・サイズの引数を取得するのが非常に困難だからとのことです。この数値は、リンカーに複数の方法で渡されることや、リンカーコマンドファイルの中にも含まれることから、複雑に関連しています。前述の背景から、現状では将来的にこの問題に関する修正の具体的な計画は無いとのことです。

従いまして、色の表示は無視して頂き、InclusiveSizeの値が設定したスタックサイズに近い場合は、設定を再度見直して頂ければと存じます。

以上、よろしくお願いいたします。

ご投稿ありがとうございます。

MSP430FR5859、コンパイラーTI v15.12.3.LTSを使っています。

同じプロジェクトをCCS6.2とCCS12で開くと、StackUsageで確認する数字が一致しない現象があります。

CCS12:mainProcessのInclusiveSizeは120

CCS6.2: mainProcessのInclusiveSizeは1532

原因は何でしょうか。

上記につきましては、CCS v12の内容が適切かと存じますが、念のためメーカーに確認させていただきますので、少々お時間頂けますと幸いです。

また、スタックサイズは今256の設定ですが、InclusiveSizeが256超える場合(黄色い表示)はスタックのオーバーフロー発生する可能性があるというサインでしょうか。この場合、スタックサイズをInclusiveSize以上の値に設定し直すべきでしょうか。

ご認識の通り、InclusiveSizeが256超える場合は、システムに合わせてスタックサイズの再設定をご検討ください。

ExclusiveSizeは、その関数が必要とするスタック量であり、その関数が呼び出す可能性のある関数は無視されます。

Inclusive Sizeは、その関数が必要とするスタック量に、その関数が呼び出すすべての関数が必要とするスタック量を加えたもので、再帰的に適用されます。つまり、f1がf2を呼び、f3がf4を呼び…というように、それぞれの関数が必要とするスタック量が加算され、Inclusive Sizeとなります。詳細につきましては、「Code Composer Studio User’s Guide – 6.8.5. Stack Usage View」を合わせてご参照ください。

以上、よろしくお願いいたします。

本件、ご回答が遅くなり大変申し訳ございません。

メーカーへ確認させて頂いた結果、TI 社としては、推奨されるパワーダウンシーケンスに違反した場合の特定の故障メカニズムについて認識しておらず、回答出来かねるとのことです。最も安全な推奨事項は、SOC電源のアップ/ダウンシーケンスが満たされるようにPCB設計を変更するとのことです。

また、すべての J7 デバイスは、「突然の電源断」時のパワーダウンについて、以下の重要な推奨事項がありますので、ご確認ください。

- MCU_PORz&SOC_PORzをすぐにアサートして、SOCを既知の安全な状態にします。(ダウンタイムステップあたりJ 7あたり0 ms)

- SRAM (0.85 V) の供給は、COREとCPUの前に無効にする必要があります (0.5 ms)

- DDR IO (1.1 V) の供給は、COREの前に無効にする必要があります (0.5 ms)

以下、メーカー原文

==============

TI is not aware of specific fail mechanisms when violating the recommended power down sequencing. The safest recommendation is to modify the PCB design such that the SOC power up/down sequencing is met.In addition, all J7 devices have the following key recommendations for power down in “abrupt power loss”:

1. Assert MCU_PORz & SOC_PORz immediately to put SOC in a known safe state. (0ms per J7 per down time step)

2. SRAM (0.85V) supplies should be disabled before CORE & CPU. (0.5ms)

3. DDR IO (1.1V) supplies should be disabled before CORE. (0.5ms)

=================以上、何卒よろしくお願いいたします。

このAdviceは特に無視しても大丈夫でしょうか。

本デバイスで表示されているAdviceについては、低消費電力化(ULP Advisor)、及びパフォーマンス向上(Optimizer Assistant)のための内容となりますので、基本的には無視した場合でもデバイスは動作するかと存じます。※6.8. Analysis and Optimization Tools

今回表示されている、Port AとPort BのULP Advisorの内容に対処する場合、P1, P2, P3, P4のすべてのピンに対して設定を行う必要があります。(Advice内容の詳細は、CCS上で表示されている文章をクリックすることで確認いただけます。)

上記の貴社のコードでP1のみ処理を行っていますが、P2, P3, P4についても、未使用ピンについては全てGPIOの機能として出力方向かつLow出力に設定頂ければと存じます。

以上、よろしくお願いいたします。

こちらMSP430FR5859を使っています。データシートなどを調べでは、Portについて、

P1,P2,P3,P4,PJがあります。これらのPORTについて初期化していますが、

advice上、ProtA,Bに対して初期化すべきと書いてあります。これについて、どう対処すべきでしょうか。

ご認識の通り、MSP430FR5859にはP1,P2,P3,P4,PJがあり、PortA(PA)はP1, P2へのワード単位でアクセスする場合のグループ名となります。(PBはP3, P4に対応)。

詳細につきましては、ユーザーズ・ガイド「12.1 Digital I/O Introduction」をご参照ください。なお初期化に関しましては、こちらのサンプルコードを参考に処理頂けますでしょうか。未使用のピンについては、低消費電力化の為に、GPIOの機能として出力方向かつLow出力に設定頂ければと存じます。

以上、よろしくお願いいたします。

ご確認ありがとうございます。

お手数ですが、まずはこちらの過去類似事例を参考に、ご確認頂けますでしょうか。同様のエラー「Invalid project description.」が発生しております。

お問い合わせありがとうございます。

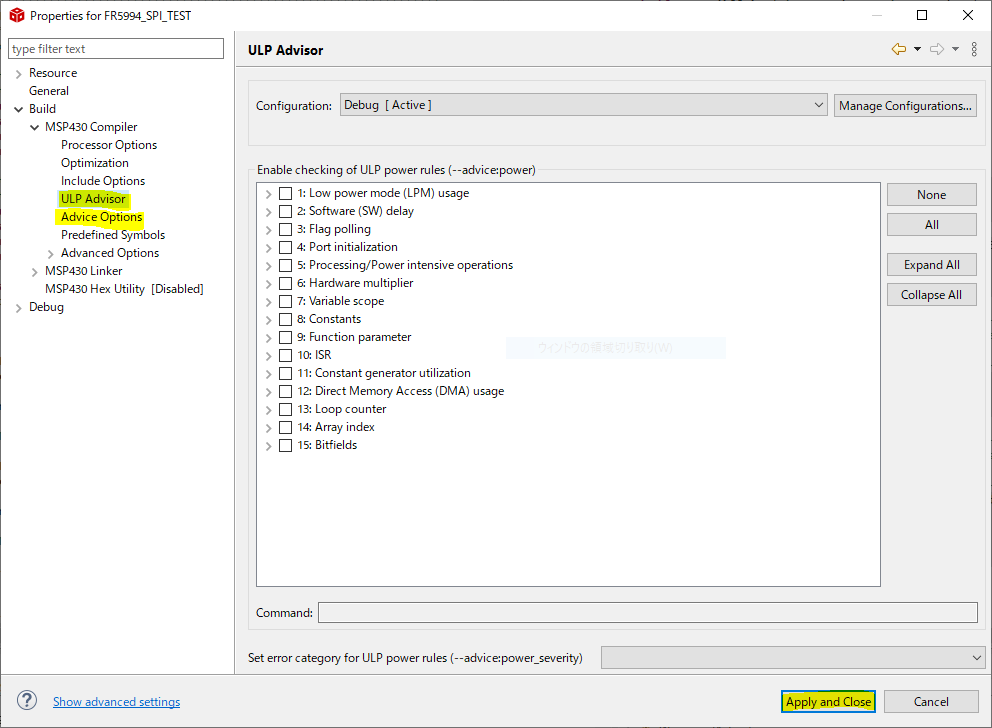

はじめに、プロジェクトを右クリックし、Propertiesを開きます。下図の通り、”ULP Advisor”及び”Advice Optin”の設定画面でチェックボックスをすべて外し、”Apply and Close”を押すことで、再Build時にAdviceの項目は消えるかと存じます。

なお、Adviceの内容については下記ULRをあわせてご参照ください。

6.8. Analysis and Optimization Tools

以上、よろしくお願いいたします。

お問い合わせありがとうございます。

デバッガを外しても、ターゲットが動作しているように見えますが、これはCCSのディフォルトな機能でしょうか。

ターゲットにロードした.outファイルは自動的にFlashに書き込んでくれているでしょうか。

上記につきましては、ご認識の通りとなります。CCSにてデバッグボタンよりデバッグを開始した場合、本製品ではデフォルトで.outファイルがFlashへ書き込まれます。

デバッグ機能の詳細につきましては、以下の資料を合わせてご参照ください。

Code Composer Studio User’s Guide – 7.3. Launching a debug session特別な設定をしていないので、正しく書き込んでいるのかは不安です。Uniflashを使って.txtファイルを書き込むのは一番確実でしょうか。

以下のURLの通り、本製品のFlahsへの書き込み方法につきましては、Uniflash、CCS、MSP-GANG等複数のツールが選択できますので、貴社のユースエースに合わせてご選択頂ければと存じます。

[FAQ] MSP430™ MCUs Development Guide Book以上、よろしくお願いいたします。

本件、ご連絡が出来ておらず大変申し訳ございません。

現時点でメーカーより回答がいただけておらず、何度か催促している状況となります。回答が有り次第ご連絡させて頂ければと存じますので、大変恐縮ですが、もう少々お時間頂けますと幸いです。

以上、何卒よろしくお願いいたします。

お問い合わせありがとうございます。

頂いたご質問についてはメーカーに確認させていただきますので、大変恐縮ですが少々お時間頂けますと幸いです。

なお、返答内容によっては、直接メールにてご連絡させて頂きますが、予めご容赦ください。

以上、よろしくお願いいたします。

ご投稿ありがとうございます。

AWR1843BoostではTM4C1294xはXDS110として動作させていました。

私の場合だとTM4C129ENCZADにXDS110を搭載すべきでしょうか?

それともそういうものは搭載せずともUARTとJTAGとUSBさえ開通できればよろしいでしょうか?

TM4C129ENCZAD,とXDS110(TMDSEMU110-U)は別々の製品となります。

XDS110はJTAGデバッグプローブ及び、PCと接続するためにUART-to-USB変換を行う製品となります。AWR1843Boostでは、搭載されているTM4C1294NCPDTがXDS110の役割を担っております。

貴社のボード上に実装されているAWR1843に対し、

- 基板上にJTAG通信、UART-to-USB変換機能を持たせる場合は、基板上にTM4C1294NCPDTを実装していただければと存じます。

- 基板外にJTAG通信、UART-to-USB変換機能を持たせる場合は、XDS110別途用意いただき、外部から接続できるよう専用のコネクタを実装いただければと存じます。

以上、よろしくお願いいたします。

- What behaviour happen these MSP-GANG error?

-

投稿者投稿