- 公開日:2022年01月31日

- | 更新日:2024年03月28日

押さえておきたいDRAMの基礎 Part 1: 読み書きの原理と内部構造

- ライター:Takahashi

- メモリー

はじめに

押さえておきたいDRAMの基礎について2回にわたり紹介します。今回はPart 1として、読み書きの原理と内部構造についてです。Part 2では、今回の内容を踏まえた上でコマンドとシーケンスについて紹介していますので、こちらも合わせてご確認ください。

押さえておきたいDRAMの基礎 Part 2: コマンドとシーケンス

DRAMとは?

DRAM(Dynamic Random Access Memory)は、電源を供給しているときのみデータを保持できる揮発性のメモリーで、プロセッサーが実行中のプログラムや演算データを一時的に保存しておく、主記憶装置として使用されます。代表的な不揮発性メモリーには、他にもSRAMなどがありますが、近年様々な分野で高い処理能力、大容量化が求められており、比較的安価に大容量が実現できるDRAMは幅広いシステムで使用されています。

DRAMの種類

DRAMは世代の発展を通し、性能が向上しています。同期式DRAMの元祖であるSDRAMは、最大速度が66~166Mbpsでしたが、その後DDR(Double Data Rate)インターフェースに変わり、速度は倍々で向上していきます。また、電源の低電圧化も進み、現在主流のDDR4では最大速度3200Mbps, 電源電圧1.2Vを実現しています。これらのSDRAMの技術仕様はJEDEC標準として規定されており、異なるメーカー間においても高い互換性を持っています。

表1: DRAMの種類と基本仕様

| 項目 | SDR SDRAM | DDR SDRAM | DDR2 SDRAM | DDR3/3L SDRAM | DDR4 SDRAM |

|---|---|---|---|---|---|

| データレート | 166Mbps | 400Mbps | 800Mbps | 2133Mbps | 3200Mbps |

| 容量 | 64Mb-512Mb | 64Mb-1Gb | 128Mb-4Gb | 512Mb-8Gb | 2Gb-16Gb |

| バス幅 | x4, x8, x16, x32 | x4, x8, x16 | x4, x8, x16 | x4, x8, x16 | x4, x8, x16 |

| 電源電圧 | 3.3V | 2.5V | 1.8V | 1.5V/1.35V | 1.2V |

| I/O | LVCMOS | SSTL-25 | SSTL-18 | SSTL-15/135 | SSTL-12 POD-12 |

| プリフェッチ | – | 2n | 4n | 8n | 8n |

| バースト長 | 1, 2, 4, 8, full page | 2 | 4 | 8 | 8 |

| Bank | 4 | 4 | 4, 8 | 8 | 16, 8 |

| Bank Group | 0 | 0 | 0 | 0 | 4, 2 |

| パッケージ | TSOP BGA | TSOP BGA | BGA | BGA | BGA |

セルの構造/仕組み

メモリーセル

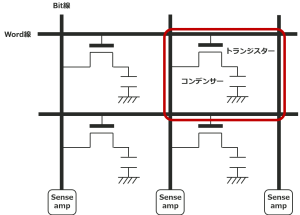

データを保存するDRAMのメモリーセルはトランジスター1つとコンデンサー1つで構成されており、各セルに対し、Bit線とWord線が対応しています。Word線はトランジスターのゲートに接続されており、Word線に電圧を印可することでトランジスターがONとなり、コンデンサーがBit線と接続されることでデータのやり取りができるようになる仕組みです。このBit線とWord線を個別に選択することにより、1つ1つのセルに対し、ランダムアクセスが可能になります。

図1: メモリーセル

読み込み/書き込み原理

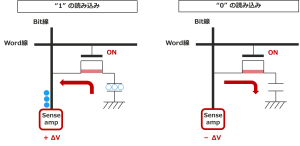

データの読み込みは、トランジスターをONにし、メモリーセルを構成しているコンデンサーの電荷がBit線と共有されることで生じるBit線の電位変化を検出することでおこないます。コンデンサーに電荷がある場合、トランジスターをONにすると、Bit線に電荷が流れ込み、Bit線の電位が一時的に上昇します。コンデンサーに電荷がない場合、トランジスターをONにすると、Bit線からコンデンサーへ電荷が流れ込み、Bit線の電位が一時的に降下します。

図2: 読み込み原理

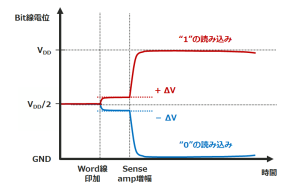

Bit線の電位変化はわずかであるため、“1”, “0”を判定するためにはBit線に接続されているセンスアンプで増幅する必要があります。Bit線の電位上昇が+ΔVであればVDDまで増幅し、-ΔVであればGNDまで増幅し、それぞれ”1”, “0”を判定しています。

図3: センスアンプによるBit線の電位変化の増幅

データの書き込みは、コンデンサーに電荷を充電または放電することでおこないます。”1”の書き込みは、Word線の電圧を上げた状態でBit線を経由してコンデンサーに充電し、”0”の書き込みは、Word線の電圧を上げた状態で、Bit線を経由してコンデンサーの電荷を放電させます。

図4: 書み込み原理

リフレッシュ

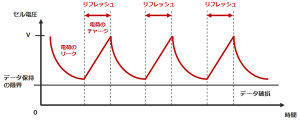

DRAMの特徴の1つとして、リフレッシュという必須動作があります。リフレッシュとは、メモリーセルに電荷を補充する動作のことです。DRAMは電源を投入しているときでも時間経過に伴い少しずつメモリーセルであるコンデンサーから電荷がリークしてしまうため、定期的に電荷を補充しなければなりません。DRAMのDynamicは、この動的なリフレッシュ動作に由来しており、DRAMがデータを保持するためには、リフレッシュをおこなうことが前提になっています。

図5: 電荷のリークとリフレッシュ

構造と内部処理

メモリーアレイ

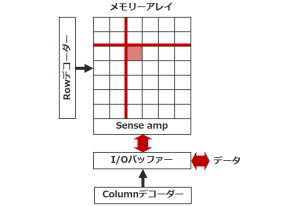

DRAMのメモリーアレイは、Word線とBit線が格子状になっており、その交差点にメモリーセルが配置されています。目的のセルにアクセスするときは、入力したアドレスに応じ、RowデコーダーではWord線の選択、ColumnデコーダーではBit線の選択をおこないます。読み込みのとき、データは指定のアドレスからI/Oバッファーを介し出力されます。書き込みのときは、データはI/Oバッファーを介し指定したアドレスに書き込まれます。

図6: メモリーアレイ

Bankとプリフェッチ

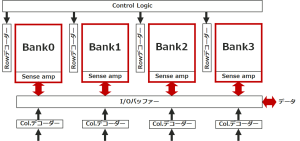

DRAMの内部は複数のBankで分割された構成となっており、アクセスしたBankが処理中であっても別のBankにアクセスする準備をすることで効率的にアクセスができ、レイテンシーの低減を実現しています。

図7: Bank構造

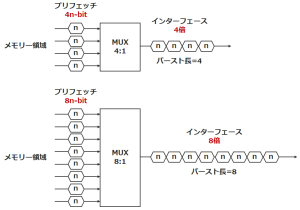

また、DRAMはプリフェッチをおこなうことで高速データ転送を可能にしています。プロセッサーの高速化に伴い外部からの入力クロックは高速化していますが、DRAMの内部での動作時間は世代を通して大きく変わっていません。この外部クロックと内部動作の差を埋めているのがプリフェッチ機能になります。プリフェッチとは、メモリーセルから事前に複数のデータをバッファー(MUX)に先取りしておくことです。内部ではこれらを一気にシリアル変換しバースト転送をおこないます。プリフェッチが4n-bitであれば、インターフェースは内部動作に対し4倍の速度で動作していることになります。

図8: プリフェッチの仕組み

インターフェース

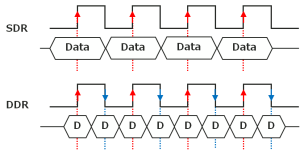

DRAMは同期式のメモリーで、クロックに同期して動作します。クロックの同期方法としてSDR(Single Data Rate)とDDR(Double Data Rate)があり、SDRはクロック1サイクルに対しデータを1つ、DDRはクロック1サイクルに対しデータを2つ転送できます。具体的には、SDRはクロックの立ち上がりエッジにのみ同期しますが、DDRではクロック(DQS)の立ち上がりエッジと立ち下がりエッジの両方に同期してデータ転送をおこなうことでクロック周波数の2倍の速度でデータ転送することが可能です。

図9: SDR/DDRインターフェース

おわりに

今回はDRAMの内部構造について紹介しました。Part 2では、よりユーザーが意識すべき内容であるコマンドとシーケンスについて紹介していますので、合わせてご確認ください。

押さえておきたいDRAMの基礎 Part 2: コマンドとシーケンス

マクニカ取り扱いメーカー・マイクロン社の最新製品とDRAM製品ラインアップはこちら。

SDRAM,DDR,DDR3,DDR3

LPDDR4/4X SDRAM

DDR5 SDRAM

Micron社のDRAM製品をお探しの方は、以下の製品ページもぜひご覧ください。