- 公開日:2025年04月07日

- | 更新日:2025年04月25日

マイコン外付けメモリについて 【DRAM編】

- ライター:乘松 誠志

- メモリー

本稿ではマイコンと共に基板に搭載されることが多い揮発性メモリであるDRAMについて、その構造・用途およびルネサス製マイコンのDRAMサポート状況をご紹介します。

揮発性メモリとは

半導体素子によって構成された記憶装置が半導体メモリですが、記憶保持観点から、揮発性メモリと不揮発性メモリに分類できます。

揮発性メモリは電源を切ると記憶が失われるメモリです。代表的なものとしてDRAM、SRAMがあります。テンポラリーデータを格納する用途で使われ、一般に不揮発性メモリよりも容量は少ないですが、高速な読み書きが可能です。

これに対し不揮発性メモリは電源を切っても記憶が失われないメモリです。代表的なものとしてEEPROMやNAND / NORフラッシュメモリがあります。

本稿ではSRAMの詳細と不揮発性メモリについては割愛させていただきます。

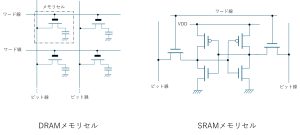

DRAM(Dynamic Random Access Memory)の構造

1メモリセル内に トランジスタ1個、コンデンサ1個を持っています。

ワード線、ビット線の電位をコントールしメモリセル内のコンデンサの充放電を行う方式により、充電された状態=1、放電された状態=0として論理を記憶します。

1メモリセル内にトランジスタ6個を持つSRAMに比べ小面積のため、安価に大容量化が可能ですが、書き込みの際コンデンサの充放電を行う必要があるため、処理速度としてはSRAMより遅いです。また、コンデンサから充電した電荷が抜けていくため、64mS以内(JEDEC(*1)で規格化された時間以内)に電荷の再充電を行う必要があります。この再充電のことをリフレッシュといい、DRAMには別途リフレッシュ用の回路が必要です。

(*1) Joint Electron Devices Engineering Council: 電子部品や半導体の標準規格を策定する国際的な標準化団体

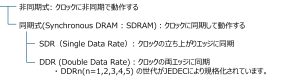

コンデンサの充放電の速度はプロセスが進んでも大きくは改善できないため、DRAMでは以下のような技術を導入して高速化を実現しています。

・クロックに同期したアクセスを行う → クロック周波数向上に伴い性能向上

・メモリセルアレイを複数Bankに分割し、同時アクセスする → 並列アクセスによる性能向上

・データバッファを設け、そこにプリフェッチしたデータをアクセスする → 先読みによる性能向上

次章で、上記の高速化技術の観点からDRAMの分類を行います。

DRAMの分類

DRAMはアクセス動作とクロックの関係により、下記に分類できます。

SDRAMのSDR/DDRの規格について以下にまとめます。各世代間で互換性はありません。

()で記載している、末尾がLである省電力版も存在しますが、これらは後述のLPDDRとは別物であることにご注意下さい。

| 世代 | プリフェッチ | データレート最大値 | Bank数 | VDD | リリース時期 |

| SDR | なし | 133 MT/s | 4 Bank | 3.3 V | |

| DDR | 2 bit | 400 MT/s | 4 Bank | 2.5 V | 2000年 |

| DDR2 | 4 bit | 800 MT/s | 4 or 8 Bank | 1.8 V (DDR2L 1.5 V) |

2003年 |

| DDR3 | 8 bit | 1600 MT/s | 8 Bank | 1.5 V (DDR3L 1.35 V) |

2007年 |

| DDR4 | 8 bit | 5100 MT/s | 16 Bank

(4Bank x 4Group) |

1.2V

(DDR4L 1.2V) |

2014年 |

| DDR5 | 16 bit | 6400 MT/s | 32 Bank

(4Bank x 8Group) |

1.1V | 2019年 |

また、DDR規格とは別に、LP(Low Power)DDRの規格もJEDECにより策定されています。こちらも各世代間で互換性はありません。

| 世代 | プリフェッチ | データレート最大値 | Bank数 | VDD | リリース時期 |

| LPDDR1 | 2 bit | 400 MT/s | 4 Bank | 1.8 V | 2006年 |

| LPDDR1E | 533 MT/s | ||||

| LPDDR2 | 4 bit | 800 MT/s | 8 Bank | 1.2V, 1.8V | 2009年 |

| LPDDR2E | 1067 MT/s | ||||

| LPDDR3 | 8 bit | 1600 MT/s | 8 Bank | 1.2V, 1.8V | 2012年 |

| LPDDR3E | 2133 MT/s | ||||

| LPDDR4 | 16 bit | 3200 MT/s | 8 Bank | 1.1V, 1.8V | 2014年 |

| LPDDR4X | 4267 MT/s | 0.6V, 1.1V, 1.8V | 2017年 | ||

| LPDDR5 | 16 bit | 6400 MT/s | 16 Bank

(4Bank x 4Group) |

0.5V, 1.05V, 1.8V | 2019年 |

| LPDDR5X | 8533 MT/s | 2021年 |

DDRとLPDDRの用途ですが、消費電力面ではLPDDRの方が有利であり、スマートフォンなどのモバイル機器には専らLPDDRが使われています。一方、DIMM(Dual Inline Memory Module)やSO-DIMM(Small Outline Dual Inline Memory Module)などのメモリモジュール規格はDDRを採用しており、PCやサーバー向けのメインメモリとしてはDDRが主流となっています。

ルネサス社マイコンのDRAMサポート状況

ルネサスマ社マイコンのRZシリーズでは、主に画像データなど大容量データを一時的に保持する外付けメモリとしてDRAMをサポートしています。RZシリーズ内でもサポートするDRAMの種類は以下の表のように異なりますのでご注意下さい。

| サポートDRAM | RZ |

| 無し | N1L |

| SDR | A1H, A1L, A1LC, A1LU, A1M, N2L, T1, T2L, T2M, T2ME, A2M |

| DDR2, DDR3 | N1D, N1S |

| DDR3L, DDR4 | A3UL, G2L, G2LC, G2UL, V2L |

| DDR3L | G2E |

| LPDDR4 | G2H, G2M, G2N, G3S, N2H, T2H |

| DDR4, LPDDR4 | G3S |

| LPDDR4, LPDDR4X | V2H |

マイコンとDRAM接続時の注意点

既出のように、最近のDRAMは低電圧で動作し、かつマイコンとの通信は非常に高速であるため、PI(Power Integrity:電源電圧品質)やSI(Signal Integrity:信号品質)をケアする必要があり、PCB設計において注意が必要です。

ルネサス社からPCB Design GuideやPCB Verification Guideが発行されているマイコンがありますので、DRAMご使用時のPCB設計はそれらを参照願います。

PCBをDesign Guideに従って設計した上で、Verification Guideに従って検証することが求められています。

PCB Design GuideとPCB Verification Guideの一例は下記をご参照下さい。

RZ/T2H and RZ/N2H Groups PCB Design Guide for LPDDR4

RZ/T2H and RZ/N2H Groups PCB Verification Guide for LPDDR4

まとめ

本稿ではマイコン外付けメモリとしての切り口からDRAMをご紹介しました。

RZシリーズマイコンを使用する場合でも、アプリケーションによってはDRAMを使うことは必須ではありませんので、DRAMの必要性につきましては事前検討をお願いします。不明点が御座いましたら 弊社技術担当 までお問い合わせ下さい。