- 公開日:2018年04月27日

- | 更新日:2024年05月15日

フライバック電源を実際に作ってみよう~その1:『IC選ぶ前にトランス検討しようよ!』~

- ライター:Polnaref

- 電源

巻いてなんぼのトランス

こんにちは。

近頃AC/DC電源を自社で作りたい、というお客様が増えている気がします。先日も「5V/3Aの15W電源作りたいのですが、TIのUCC2xxxで作れますか?」とのお問い合わせを頂きました。理由を聞くと「購入品は高いから」とのこと。

そんな方に筆者から一言。。。

IC選ぶ前にトランス検討しようよ!ねぇ!(切実)

トランスの出来栄えで絶縁電源の品質は6割決定します。トランスはノウハウの塊です。インダクタンスや巻き数は机上で算出できますが、使う線材、絶縁距離、安全規格、巻構成・・・などなど、巻いて初めてわかることが多いです。最適解はありません。こればかりは経験の積み重ねが必要です。

今回の「その1」では、AC入力100~240V、出力5V/3A(15W)のフライバック電源用トランスの設計手順を紹介します。

設計をはじめる前にコアサイズを決めよう!

絶縁AC/DC電源を設計する際、最初に見積るべきなのはトランスのコアサイズです。コアサイズが十分に大きければトランスに蓄えられる電力も増え、太い線材が使用できます。しかしコアサイズが大きいと電源回路の大きさ、つまり「体積」も大きくなります。

機構設計の担当者と相談し、実装面積や部品の高さを考慮の上コアサイズを決めましょう。

半導体の動作や諸特性、注意事項等を確認する時、データシートを参照しますよね。トランスのコアにもデータシートがあり、寸法と磁性特性が確認できます。今回は電力的に余裕があり、かつ、通販サイトで在庫があったEI25コアを選択しました。コアが決まったらボビンも必要になりますので合わせて準備しましょう。

さぁ設計だ!

設計の「入口」

あるお客様から、「トランスの設計は何から計算すればいいのでしょうか?」との御質問を頂きました。トランスを設計する上で、その「流派」は無数にありますが、「どれが正解」というのはありません。世に出ている参考書や関連書籍、全て正解です。だからこそ初手が分からないという声が多くあります。

私の意見ですが、いずれかのパラメータを「えいやぁ!」と決めてしまうのが良いと思います。私はいつも2次(出力)側の電圧から2次側の巻き数を決定しています。

今回の2次側の電圧は5Vとしました。2次側の巻線はこの5Vに加えて、整流用のダイオードの順方向電圧(Vf)を考慮する必要があります。Vfはショットキーバリアダイオードなら0.5V、ファストリカバリーダイオードなら1V程度です。今回はショットキーバリアダイオードを使用することにしましたので、2次側の巻線は5.5Vを出力するようにします。安直ですが2次側の巻き数をは6Ts(Turns)としました。

1Ts当りの出力電圧は

となり、約1Vということでなんとなく分かり易い気がします。巻き数は基本的に整数のみです。0.5巻きのテクニックもありますが、トランスの構造が煩雑になり、更に見栄えが悪いので今回はやりません。

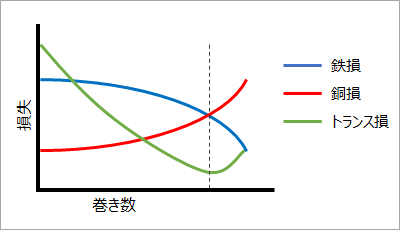

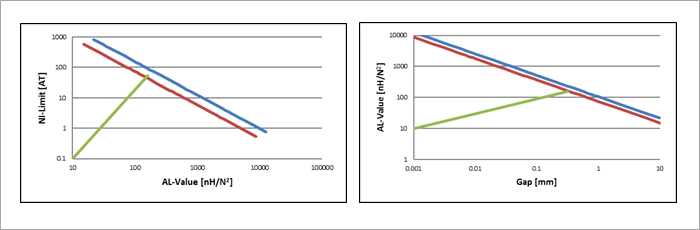

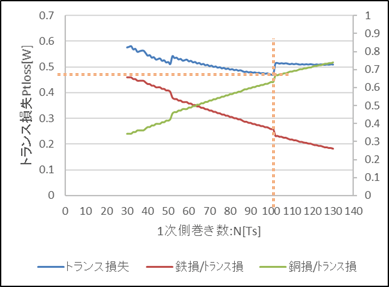

因みにこれらのパラメータは、最もトランス損失が小さくなる巻き数とギャップ長の算出にかかわってきます。トランス損失は鉄損(コアの励磁/消磁による損失)と銅損(巻線の抵抗成分と電流による損失)の和です。1次巻き数が多いと鉄損は小さくなりますが、銅損が増えます。トランス損失は鉄損と銅損の比率が1:1で最小になります。

制限及び条件を決める

入力電圧は一般的な商用AC電圧、85~264Vとします。

スイッチング周波数を早くすると、1周期に蓄えるべき電力が下がるため、コアサイズを小さくすることが可能になりますが、1次(入力)側FETのスイッチング回数が増えるためFETのスイッチ損が増え、更に制御ICにはタフな電流ドライブ能力が求められます。逆にスイッチング周波数を遅くし過ぎて可聴域(20kHz以下)にしてしまうと、今度は”コイル鳴き”が発生してしまいますので使い物になりません。そこでスイッチング周波数の上下限を設定します。今回は30kHz(min),110kHz(max)とします。

次に実現したい効率を決定します。つまり要求仕様です。今回は85%以上とします。

1次側制御ICの電源(Vaux)も必要です。フライバックコントローラICではFETを確実にONするために、電源電圧を10V以上にしている物が多く有ります。今回は14V(Vf0.5Vを除く)とします。

前提条件をまとめるとこのようになります。

| パラメータ | 数値 | 単位 |

|---|---|---|

| Vin(DC) | 120.208 | V |

| 169.706 | V | |

| 373.352 | V | |

| Vout+Vf | 5.500 | V |

| Iout | 3.000 | A |

| Vaux+Vf | 14.500 | V |

| η | 0.850 | – |

| Pout | 13.500 | W |

| Pin | 15.882 | W |

| Ploss | 2.382 | W |

複雑に絡み合うトランスパラメータ

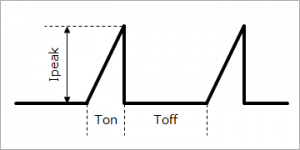

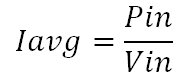

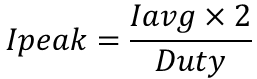

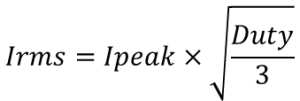

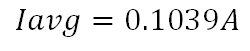

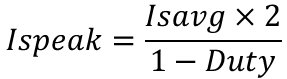

1次側の電流を算出します。電流は三角波又は台形波になりますが、今回は三角波を前提に計算します。平均値(Iavg)、尖頭値(Ipeak)、実効値(Irms)は下記の式にて導出できます。

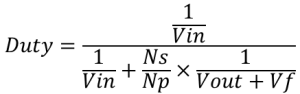

ここでDutyが必要になります。DutyとはTonとToffの比率のことです。Dutyとスイッチング周波数は1次と2次の巻き数比で決定されます。なので、トランスの検討より先にICを選ぶこと自体、手順が逆なんですね。ちなみにDutyは下記の式にて算出できます。

今度は1次巻き数(Np)が出てきました。(Nsは2次巻き数です。)上にも書きましたが、Npは非常に大切なパラメータです。「えぃやぁ!」では決められません。なので、1Tsずつ増やして計算します。今は取り敢えずNp=50Tsとしましょう。Nsは先ほど6TsとしましたのでDutyは21.26%になり、各1次側電流は

となります。

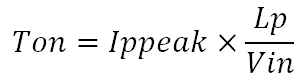

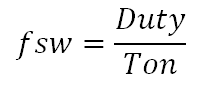

Dutyが分かればスイッチング周波数(fsw)も知りたくなります。fsw=Duty/TonなのでTonを求めます。更にTonはLpに依存するので、、、

こんがらがってきました。ちょっと整理しましょう。ここからの算出する順番は下記の通りです。

- ギャップ長lgの決定

- Lpの算出

- Tonの算出

- fswの算出

- 2次側電流の算出

- コアパラメータより鉄損を算出

- 巻き数と線径から銅損を算出

- トランス損失の算出

ギャップ長は任意の値なので、Npと同様に少しずつ増やしながら、損失が最小値となる構成を選びます。

Npが変われば損失が最小値となるギャップ長も変わりますので、Npを1turn増やすご度にギャップ長を5umから4mmまで5umずつ増やしていって… とか

そんなのいちいちやってられません。

電卓でちまちまやっていたら精神が崩壊してしまいます。

なので、エクセルに計算式を組み込んだ「トランス設計計算ファイル」の作成をお勧めします。電源設計者の約半数はこれまでの勘と経験から「ドンピシャ」で設計し、半数は設計ツールを独自に作成しているようです。

以前、知り合いの設計者の方に計算ファイルを見せて頂きましたが、非常にクセが強く、さっぱりわかりませんでした。本人曰く、「俺が作ったから俺にしか使えない」とのこと。読者の皆様も、自分ONLYの設計ツールを作ってみてください。

各パラメータの算出、決定方法

設計の際に必要となる各パラメータの算出/決定方法は以下の通りです。

ギャップ長(lg)

任意の値(0.1~4.0mm)

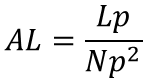

1次側インダクタンス(Lp)

1次側FETのTon

スイッチング周波数(fsw)

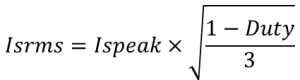

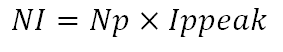

2次側電流パラメータ

NIリミット

AL-Value

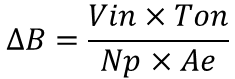

磁束密度(ΔB)

鉄損(Pcore)

![]() ※係数は使用するコアにより異なります。

※係数は使用するコアにより異なります。

銅損(Pwire)

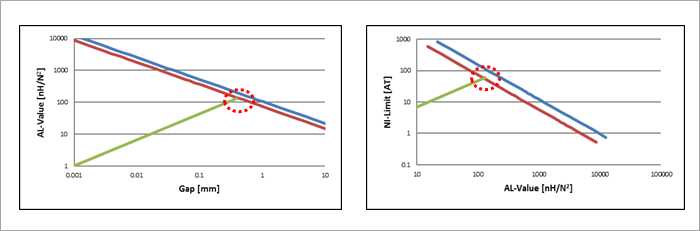

NIリミット、AL-Value、Pcvはコアのデータシートから読み取りました。NIリミットとAL-Valueは、コアが飽和する限界点を表わしています。

青はデータシートからの読み取った値、赤は青の30%低減値、緑の右先端は本仕様における計算値を表わしています。緑の右端が青を超える場合、定格動作においてトランスが飽和し、1次側巻線に大電流が流れる恐れがあります。その場合にはトランスのサイズを見直すか、鉄損を増やす代わりにNpを巻き減らすorギャップを小さくするしかありません。なので、はじめに使用可能なトランスの大きさを検討し、「そもそもAC/DC電源の電気的要求仕様と機構的要求仕様は妥当なのか」を判断するんですね。

経験を積めば「出力電力とそれに必要なトランスコアの体積」が予測できるようになるでしょう。

設計結果

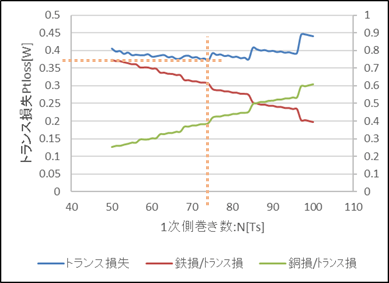

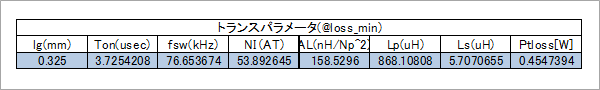

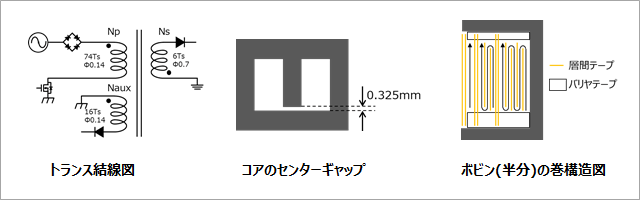

EI25コアで15W(5V/3A)出力の電源を作る際、最も損失が小さくなるNpとNsはそれぞれ、

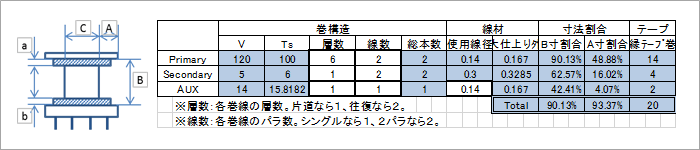

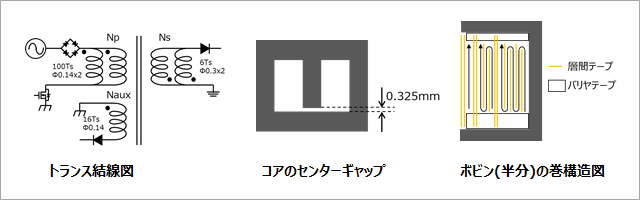

φ0.14mmで74Ts、φ0.7mmで6Tsであることが分かりました。また、他のトランスパラメータは以下の通りです。

因みに、「A寸」のトータルが100%近くになると、「巻太り」により、コアが嵌らないことがあります。余裕を持った寸法設計を心掛けてください。上記計算では96.34%(ワースト値)なので、正直ギリギリですね。

これらの結果からトランスの略図を描いてみました。

1次-2次間の沿面距離は、汚損度Ⅱ(屋内)、材料グループⅠ(CTI≧600V)、実効値動作電圧400V以下、IEC-J60950準拠を条件に、2mmとしました。沿面距離や空間距離、一般安全規格については、経済産業省のHPをご参照ください。

作れなかったら意味が無い

さて、何とか数字的にはトランスが作れそうな雰囲気が漂ってきました。が、ここで一つ問題があります。

φ0.7mmのエナメル線なんて巻けないよ!

巻いたことがある人にはわかるのでしょうが、線材は太くなるに連れ巻き辛くなります。また、線材の屈曲や巻線の折り返しにて余分な体積(巻スペース)を消費しますので、「巻乱れ」等の品質トラブルの原因になることもあります。

個人的には、φ0.3mmが人間の素手で無難に巻くことができる限界だと思っています。また、線種も少なくしたいので、今回はφ0.14mmとφ0.3mmのみを使用します。

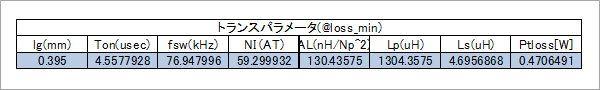

これに合わせて再計算した結果がこちら。

線径がφ0.7mmからφ0.3mmに変更になったことにより、トランス損が16mWほど増えてしまいましたが、まぁ良しとしましょう。

Npが74Tsから100Tsになり、NIリミット値も上がっています。AL値とNI値は磁化飽和の目安になります。

Npが増えたことでNI値の増加を危惧していましたが、AL値が抑えられた分、飽和の心配はなさそうです。

しかし100Tsかぁ、、、

ICを選定

やっとここでICを選定します。

選定する目安は、スイッチング周波数(max):77kHz以上、Ton(min):4.5usec未満、Vdd:15~20V程度、ということで、Texas Instruments社(以降、TI社)のUCC28630を選定しました。

UCC28630はHV Start UP機能を有していますので、個別の起動回路は不要、設計を簡素化できます。また、UVLOが8VなのでVauxが大きく変動してもすぐに異常停止することはありません。更に、評価ボードには既にダイオードブリッジやCMCが実装されていますので、お得感があります。

UCC28630EVM-572

ボビンのピンアサイン

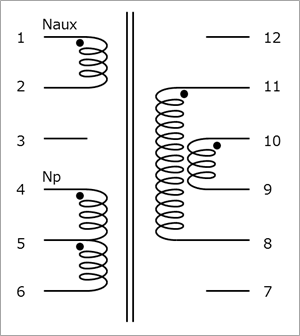

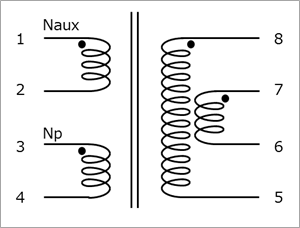

今回作成するトランスはTI社の評価ボードUCC28630EVM-572に実装して動作検証することにします。評価ボードのトランスのピンアサインは下図のようになっています。

ボビン(12ピン)結線図

評価ボードのトランスは12ピンであるのに対し、今回購入したコアとボビンのセットは8ピンでした。更にピンのピッチも異なるため、そのまま実装はできません。そのため、下図のように作ることにしました。

ボビン(8ピン)結線図

次回

今回はここまでです。その2では今回設計したトランスを実際に巻く模様をお届けする予定です。

巻き数が100なので、今から巻いた回数が分からなくなる自分の姿が目に浮かびます。はたして何回巻きなおしすることになるでしょうか?次回をお楽しみに!

Texas Instruments社の製品をお探しの方は、メーカーページもぜひご覧ください。

Texas Instruments社

メーカーページはこちら

フライバック電源を実際に作ってみよう

フライバック電源を実際に作ってみよう~その1:『IC選ぶ前にトランス検討しようよ!』~

フライバック電源を実際に作ってみよう~その2-『トランスを巻いてみた』