ホーム › フォーラム › Texas Instruments › オーディオ › TLV320AIC3109-Q1について

このトピックには6件の返信が含まれ、2人の参加者がいます。5 年、 10 ヶ月前に ishi1126 さんが最後の更新を行いました。

-

投稿者投稿

-

TLV320AIC3109-Q1について

デバイス型番:TLV320AIC3109-Q1TI製TLV320AIC3109-Q1のレジスタ設定について、

以下のように設定していますが、問題無いかご確認頂けないでしょうか。通信時の波形を添付致します。

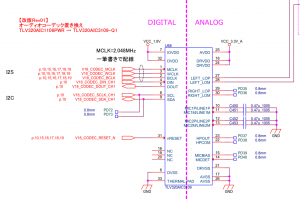

回路図も添付致します。また、Register 0にアクセスした後にreadが推奨されていますが、

readしないで続けてアクセスすることは可能でしょうか。以下の設定としています。

・DSPモード

・Fs(ref)=48KHz

・FS=8KHz

・MCLK=2.048MHz

・TDM Offset = 1

・Right Channel = all’0′

・256クロックモード

・Left Justified【レジスタ設定 Page0のみ】

————————————————————

Register 書き込みデータ

3~0 91 AA 00 00

7~4 08 00 00 C0

11~8 01 00 40 00

15~12 00 00 00 00

19~16 84 FF FF 80

23~20 78 78 08 78

27~24 02 00 00 78

31~28 00 FE 00 C0

35~32 00 00 00 80

39~36 00 00 80 00

43~40 00 64 00 00

47~44 00 00 00 80

51~48 04 00 00 00

55~52 00 00 00 00

59~56 00 04 00 00

63~60 00 00 00 00

67~64 00 00 04 00

71~68 00 00 00 00

75~72 00 00 00 04

79~76 00 00 00 00

83~80 00 80 00 00

87~84 00 08 00 00

91~88 00 00 00 00

95~92 00 00 00 00

99~96 00 00 00 00

103~100 00 02 00 00

107~104 00 00 00 00

111~108 00 00 00 00

115~112 00 00 00 00

119~116 00 00 00 00

123~120 00 00 00 00

127~124 00 00 00 00

————————————————————Attachments:

ishi1126 様

お問い合わせ頂きましたTLV320AIC3109-Q1のRegister設定に関しまして

対象の製品はAudio Codecになりますので、ご使用の目的に応じて

適切な設定が必要になります。

そのため、AEC-Q100には対応しておりませんが、評価Boardと専用GUIが

用意されておりますので、そちらをご活用頂くことを推奨致します。

あいにく弊社にこの評価Boardがなく、ご提供頂きましたたRegister設定を

実機で確認することが出来ません。TLV320AIC3109-Q1 Evaluation Module and USB Motherboard

http://www.ti.com/tool/TLV320AIC3109EVM-KPage 0のRegister 0でPageの選択を行いますので、誤って異なるPageで

Read/Writeすることがないように現在のPage確認を推奨しております。Kato

ご回答頂き有難う御座います。

いろいろ試した結果動くようになりました。

なお、データシートのP74のRegister 86にて、

LEFT_LOP/M Power StatusがRead Onlyになっていますが、

評価基板を参考に’1’を書きこむことで動作しました。恐らく、『R』ではなく『R/W』かと思います。

続けて申し訳御座いません。

下記の件についてメーカー様にご確認頂けないでしょうか。状況として、すでにTLV320AIC3109-Q1を搭載した基板をデバッグしており、

DACは動くようになったのですが、ADCの動作に問題がある状況です。データシートのReservedを書き換えることで波形が改善している状況で、

メーカー様にReservedなど書き換える必要のあるレジスタを確認したいです。

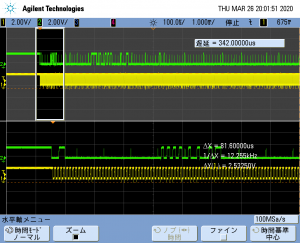

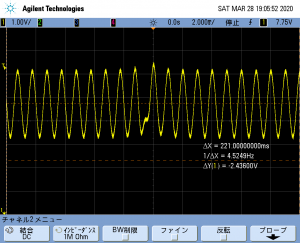

(2020年3月27日の返信の通り、Read Onlyを書き換えることで改善しているため、データシートの記載ミスなどを疑っております)添付の『波形1』は正常なSIN波をMIC1P/LINE1PとMIC1M/LINE1Mに入力し、

DOUTとDINをループバックし、LEFT_LOPから出力した波形になります。

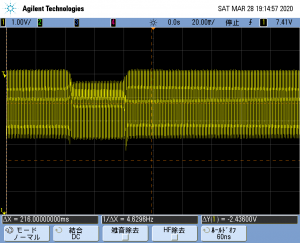

画像の通り、Reservedを書き換える前は長期間、歪みが発生しております。添付の『波形2』は評価基板を参考にReservedのRegister 22を0x78⇒Ox84とすることである程度改善しました。

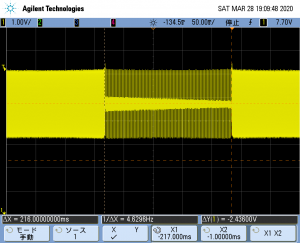

ただし、それでも約216ms周期で歪みが発生します。『波形3』は『波形2』の拡大になります

お手数ですが、ご確認のほど宜しくお願い致します。

ishi1126 様

Register 86の「LEFT_LOP/M Power Status」に関しましてはご指摘の通り、

Status Registerではなく、Control Registerであり、R/Wになります。

正しいStatus RegisterはRegister 94の「LEFT_LOP/M Power Status」です。

Data Sheetの改版が遅れており、申し訳ございません。Kato

ishi1126 様

LEFT_LOPの出力歪みに関しまして以下の項目をご確認頂き、

情報をご提供下さいますよう、宜しくお願い致します。<ご確認事項>

(1) 回路図について

・各電源端子にDecoupling Capacitorの記載がないようですが、Device直近に

高周波用と低周波用のCapacitorが実装されておりますでしょうか?・各Clock Lineにダンピング抵抗が挿入されていないようですが、

送信回路側に挿入されておりますでしょうか?・LEFT_LOP/Mの負荷は何になりますでしょうか?

後段にClass-D Ampが接続されている場合、Codecによって生成される帯域外Noiseが出力されるため、

30kHz程度のLPFを追加することを推奨致します。(2) 各Clock波形の追加取得

・BCLK、WCLK、DINについて位相関係がわかるレベルのScreenshotを取得願います。Kato

ご連絡頂き有難う御座います。

返事が遅れて申し訳御座いません。

本件ですが、I2S側のデータ形式に間違いがあることが原因でした。

データ形式を修正することで歪みが無くなっております。ご対応頂き有難う御座います。

-

投稿者投稿

オーディオ

オーディオ