ホーム › フォーラム › Texas Instruments › マイコン › C2000 › 5.9.1 Power Sequencingについて

このトピックには9件の返信が含まれ、2人の参加者がいます。5 年、 10 ヶ月前に ![]() Ge さんが最後の更新を行いました。

Ge さんが最後の更新を行いました。

-

投稿者投稿

-

5.9.1 Power Sequencingについて

デバイス型番:TMS320F28375S5.9.1.1 Signal Pin Requirementsに下記要件が定められているかと思います。

Before powering the device, no voltage larger than 0.3 V above V DDIO can be applied to any digital pin,

and no voltage larger than 0.3 V above V DDA can be applied to any analog pin (including V REFHI ).電源起動前にVDDIO+0.3Vを超過する電圧を印加してはいけないという内容になっていますが、

電源遮断時は問題ないと考えて良いでしょうか。例えばVDDIO供給源として電源A、VREFHI供給用に電源Bを用意したとします。

この時、電源A.Bの大元の電源が遮断された場合、電源A出力電圧が先に低下し、

電源B出力電圧 > 電源A出力電圧+0.3Vになることもあるかと思います。

仮に電源A,Bの出力間に保護用にダイオードを設けたとしても

順方向降下電圧は電流値に依存して増大するため、

完全な保護は難しいと考えられます。「Before powering the device」に電源遮断時は含まない、と考えると

上記課題がなくなってありがたいのですが、いかがでしょうか。また、5.9.1.3 V DD Requirementsに

During the ramp, V DD should be kept no more than 0.3 V above V DDIO .とありますが、

「During the ramp」はランプ立ち上がりの間であって、遮断時は含まないと考えて良いでしょうか。ET様

お問い合わせありがとうございます。

本件、データシートからはパワーダウン時にも適用されるものか判断ができなかったため、メーカーに確認致しました。その結果、パワーアップ時、パワーダウン時ともにこの規定(VDDIO+0.3Vを超過してはならない)を守るようにしなければならないとのことでしたので、そのように設計をお願いできますでしょうか。

以上、宜しくお願い致します。

ご回答くださりありがとうございます。

下記URLの評価ボードの回路図を拝見しましたところ、

保護ダイオードがあるようには見受けられません。

http://www.ti.com/lit/ug/sprui25d/sprui25d.pdfP10によると3.3Vから1.2Vを作られていますが、

この構成であれば遮断時も要件を満たすと考えて良いでしょうか。

あるいは問題があるのであれば推奨構成をご教示頂きたく思います。お問い合わせありがとうございます。

評価ボードは、あくまでも評価用で、設計を保証するものではございませんので、デバイスのデータシートの規定を満たしていない可能性が御座います。

推奨構成については改めてメーカーに確認致しますので、少々お待ちいただけますでしょうか。

以上、宜しくお願い致します。

お問い合わせいただきました電源回路ですが、ご認識いただいております通り、評価ボード(LaunchPad)の電源回路は保護ダイオード等がないため、3.3V、1.2Vのラインの負荷の状態によってはデータシートの規定を満たせない可能性が御座います。

尚、C2000wareの以下の回路であれば、データシートの規定を満たせると考えますので、こちらをご参照いただけますでしょうか。

C:\ti\c2000\C2000Ware_3_01_00_00\boards\controlCARDs\TMDSCNCD28379D\R1_3

こちらの回路では、電源IC(TPS62420)を使用し、5Vから3.3Vと1.2Vを出力しており、且つ3.3Vと1.2Vの間に保護ダイオードが接続されております。

以上、宜しくお願い致します。

ご回答くださりありがとうございます。

>「C:\ti\c2000\C2000Ware_3_01_00_00\boards\controlCARDs\TMDSCNCD28379D\R1_3」

ローカルファイルへのパスとなっているため、

ネットワークへのパスをご教示頂くか、ファイルをアップロードいただけると大変助かります。>保護ダイオード

品番確認できていないため、憶測で恐縮ですが、

どんなにVfが小さいダイオードでも電流値によっては0.3Vを超過するかと思います。

1.2V系に比して3.3V系の負荷が大きい場合は、3.3V系 < 1.2V系となり、

それなりの電流が流れることが考えられます。

この場合、0.3Vを超過する可能性があるかと思うのですが、

ご回答いただいた構成であれば問題ないでしょうか。ご返信ありがとうございます。

説明が不足しており申し訳ございません。保護ダイオードはあくまでも補助の目的で接続されており、ご認識の通り、負荷の状態によっては、シーケンスを守ることができない可能性が御座います。そのため、システムに併せて電源IC(TPS62420)のEN2端子の電圧などの調整をお願いします。例えば、EN2の端子の電圧を変えて、EN2のスレッショルドをより高いところにもっていくなどです。

> >「C:\ti\c2000\C2000Ware_3_01_00_00\boards\controlCARDs\TMDSCNCD28379D\R1_3」

> ローカルファイルへのパスとなっているため、

> ネットワークへのパスをご教示頂くか、ファイルをアップロードいただけると大変助かります。こちらについても説明不足で申し訳ございません。以下のC2000wareをインストールいただく、上記のフォルダが展開されますので、こちらをご入手いただけますでしょうか。

C2000ware

http://www.tij.co.jp/tool/jp/C2000WARE以上、宜しくお願い致します。

ご回答くださりありがとうございます。

>そのため、システムに併せて電源IC(TPS62420)のEN2端子の電圧などの調整をお願いします。例えば、EN2の端子の電圧を変えて、EN2のスレッショルドをより高いところにもっていくなどです。

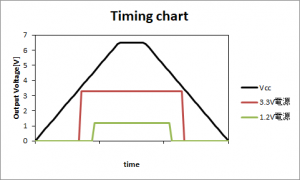

EN1,EN2端子の電圧を調節して、例えば、

3.3VはVcc=4Vで起動、1.2VはVcc=4.5Vで起動することで

3.3V<1.2Vの状態を回避するという理解で正しいでしょうか。

※添付図この場合、起動電圧が異なりますが、

5.9.1.3 V DD Requirementsは満たせるものとして考えて良いでしょうか。

・V DDOSC and V DD must be powered on and off at the same time.

VDDOSC(3.3V)とVDD(1.2V)は同時にオン/オフしなければならない。

・V DDOSC should not be powered on when V DD is off.

VDD(1.2V)がオフの時、VDDOSC(3.3V)はオンすべきではない。別のトピックで以前質問した際に、下記回答を頂いております。

>電源の立ち上がりタイミングにつきましては、特に明記はなく、

>5.9.1.2 VDDIO, VDDA, VDD3VFL, and VDDOSC Requirements、

>5.9.1.3 VDD Requirements

>に各電源が0.3Vに収まる、かつVDDはVDDIOより0.3Vを超えないことが記載されております。

>この範囲であれば、開始点は異なっていても問題はございません。

https://emb.macnica.co.jp/forums/topic/10450/

結局のところ、他の要件が満たせるのであれば

「同時にオン/オフ」は気にしなくてよいのでしょうか。ET様

お問い合わせありがとうございます。

> ば、EN2の端子の電圧を変えて、EN2のスレッショルドをより高いところにもっていくなどです。

> EN1,EN2端子の電圧を調節して、例えば、

> 3.3VはVcc=4Vで起動、1.2VはVcc=4.5Vで起動することで

> 3.3V<1.2Vの状態を回避するという理解で正しいでしょうか。

> ※添付図ご認識のとおりとなります。

> この場合、起動電圧が異なりますが、

> 5.9.1.3 V DD Requirementsは満たせるものとして考えて良いでしょうか。

> ・V DDOSC and V DD must be powered on and off at the same time.

> VDDOSC(3.3V)とVDD(1.2V)は同時にオン/オフしなければならない。

> ・V DDOSC should not be powered on when V DD is off.

> VDD(1.2V)がオフの時、VDDOSC(3.3V)はオンすべきではない。

>

> 別のトピックで以前質問した際に、下記回答を頂いております。

> >電源の立ち上がりタイミングにつきましては、特に明記はなく、

> >5.9.1.2 VDDIO, VDDA, VDD3VFL, and VDDOSC Requirements、

> >5.9.1.3 VDD Requirements

> >に各電源が0.3Vに収まる、かつVDDはVDDIOより0.3Vを超えないことが記載されております。

> >この範囲であれば、開始点は異なっていても問題はございません。

> https://emb.macnica.co.jp/forums/topic/10450/

> 結局のところ、他の要件が満たせるのであれば

> 「同時にオン/オフ」は気にしなくてよいのでしょうか。VDDとVDDOSCが同時にONできない場合には、以下のエラッタに該当し、内蔵クロック(INTOSC)が低速で動作してしまう可能性が御座います。

TMS320F2837xS MCUs Silicon Errata (Rev. H)

http://www.ti.com/lit/pdf/sprz422

INTOSC: VDDOSC Powered Without VDD Can Cause INTOSC Frequency Driftそのため、同時にONしない場合にはエラッタシートに記載の対応(外部のクロックを使用する)をお願い致します。

以上、宜しくお願い致します。

-

投稿者投稿

C2000

C2000