ホーム › フォーラム › Texas Instruments › 電源IC › 位相シフトフルブリッジ FET OUTA,B遅延設定

このトピックには7件の返信が含まれ、2人の参加者がいます。5 年、 9 ヶ月前に wtidesigner さんが最後の更新を行いました。

-

投稿者投稿

-

位相シフトフルブリッジ FET OUTA,B遅延設定

デバイス型番:UCC28950DELAB端子の抵抗 Rabの許容範囲は、13kΩ~90kΩとなっています。

OUTA-OUTB間のデッドタイムを狭めたく、抵抗を13kΩ以下に設定をしたいのですがいくらまで可能でしょうか。

またこの抵抗値制限は何からくるものなのでしょうか。軽負荷時の電源効率を上げるため、8.2kΩ~10kΩに設定希望です。

wtidesigner様

ご投稿ありがとうございます。

お問い合わせ頂いた内容についてですが、

Rabの許容範囲の下限13kΩはICの長期信頼性、上限90kΩはノイズ感度を考慮して設定されており、

Rabを許容範囲(13kΩ〜90kΩ)から外れた値に設定することは推奨されておりません。

(上記についてはTIにも確認いたしました。)また、デッドタイムを変更する方法としては、以下のデータシートp.19〜20に記載されているように

ADELピンに接続する抵抗値(RA, RAHI)を変更し、KAの値を調整する方法もございますので、

Rab=13kΩに設定して頂き、後はKAの値を変更することによりOUTA-OUTB間のデッドタイムを調整して頂けますでしょうか。

https://www.ti.com/lit/ds/symlink/ucc28950.pdf?&ts=1590138684360以上、よろしくお願い致します。

ご返信ありがとうございます。

軽負荷時ですからカレントトランスからの電圧 CS-voltageはほぼ0Vの状態。

他からバイアスをかけるしかありませんが、そうすると制御特性が変わってきてしまい

全評価がやり直しになりますが、それしか手がないという事ですね。wtidesigner様

返信頂き、ありがとうございます。

システムが何かしらの内部制限(Dmaxなど)に達しない限り、他からバイアスをかける等でCSピンの電圧を変化させても、制御特性は変化しないと考えております。

また、他にデッドタイムを変更する方法として、ADELピンに固定電圧を印加する方法(Rab=13kΩに設定)がございますが、こちらについては詳細を確認しておりますので、少々お待ちいただければと存じます。

以上、よろしくお願い致します。

wtidesigner様

昨日の回答でご紹介したADELピンに固定電圧を印加する方法(Rabは13kΩに設定)について確認致しましたので、

追加で投稿致します。

まず、OUTA-OUTB(OUTC-OUTD)間のデッドタイムはRab(Rcd)の他にADELピンの電圧VADELによって調整することが可能です。

以前回答したKAの値を調整する方法では、ADELピンがCSピンと分圧抵抗を介して接続している場合の方法であるため、ADELピンの電圧VADELは、CSピンの電圧(CS)とADELピンの分圧抵抗によって決まります。(VADEL=CS×KA)

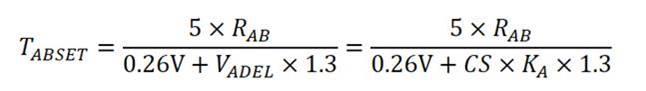

そのため、以下の式にてOUTA-OUTB間のデッドタイムを概算することが可能です。

なお、今回のようにADELピンをCSピンと分圧抵抗を介して接続せず、直接固定電圧(最大2Vが推奨)を印加することにより、CSピンの電圧に依らず、デッドタイムを調整することが可能です。

(ADELピンはCSピン同様、他からバイアスをかける等で電圧が変化しても、制御特性は変化致しません。)

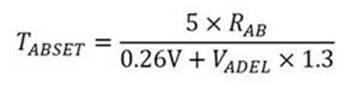

上記の方法では、VADEL には直接固定電圧を印加するため、OUTAーOUTB間のデッドタイムは以下の式にて概算することが可能です。

※上記に記載している2つの式は、外部のドライバ回路やスイッチングの応答時間の遅延などの外部遅延は考慮されておりません。

以上、よろしくお願い致します。

ご回答ありがとうございます。

ご回答いただいた回答の前者、KAの値を調整する方法は軽負荷時ですから CS=0。

よって RABできまる固定値になりますから13kΩ以下にできないのであれば、現状より TABSETは小さくすることができません。後者の固定電圧(最大2Vが推奨)を印加の方法では、出力電力増加つまりCS電圧の上昇によりAB間のTime Delyを短くすることができません。

この二つの問題を解消するためにCS電圧にバイアスをかけることを二つ目の投稿で述べたのですが、そうするとCD間,AF間,BE間のTime Delyが変わってきます。

制御特性の意味合いが異なっているようですが、各FET間のTime Delyが微妙に変わると、効率など電源特性が変わっています。このことを(電源)制御特性が変わると述べています。

例えばCS電圧にバイアスを加えると、AB間のTime Delyは短くなりますが、出力電力が増えた際のAF間Time Delyは広がってしまいます。これら全ての調整のやり直しが発生するためTABSETだけを変える方法を模索しているものです。どうも良い案はなさそうですね。

wtidesigner様

返信頂き、ありがとうございます。

ADELピンとADLEFピンがCSピンと分圧抵抗を介して接続している場合、

貴社の御認識通り、CS電圧にバイアスをかける(CS電圧を変化させる)ことで、AB間だけでなく、CD間,AF間,BE間のTime Delayの値も変化致します。また、もし他のTime Delayを変えずにTABSETだけを変化させる場合、Rab=13kΩでCS電圧(もしくはADELピンに印加する固定電圧)を設定して頂いた上で、

Rcd、Refの値を調整して、他ののTime Delayを元の値に合わせて頂く方法しかございません。以上、よろしくお願い致します。

ご回答ありがとうございました。

試しにKaを 0.5から0.75に変えてみました。若干FET AB間の中点波形の変化はありましたが、Rabを10kΩ等にするほど変わらず

軽負荷時効率の変化もわずかでした。軽負荷時効率の特性を現状で我慢するか、定数を全て調整しなおすかで考えます。

-

投稿者投稿

電源IC

電源IC