ホーム › フォーラム › Texas Instruments › オーディオ › TPA3112D1のFAULT機能について

このトピックには17件の返信が含まれ、2人の参加者がいます。5 年、 7 ヶ月前に Kato さんが最後の更新を行いました。

-

投稿者投稿

-

TPA3112D1のFAULT機能について

デバイス型番:TPA3112D1TPA3112D1の/FAULT機能について確認です。

実機で以下の短絡障害を調査した結果、(2)だけ/FAULTが発生しない結果です。これは正常な動作でしょうか。

(1)、(3)、(4)の短絡障害では/FAULT発生しています。<短絡障害>

(1)INPをGNDにショート

(2)OUTP-OUTNのショート

(3)OUTP-GNDにショート

(4)OUTP-+12.5Vのショートishi1126 様

TPA3112D1に関してOUTP-OUTN間のShortにおいて/FAULTがLowにAssertされないとのことですが、

出力間をShortした際の入力条件とShortした箇所(出力端子 or LC Filter後のSpeaker端子)をご教示頂けますでしょうか?

また、Short時のOscilloscopeの波形を共有して頂けますと幸いです。Kato

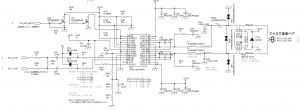

回路図を添付致します。

Shortした箇所は「LC Filter後のSpeaker端子」になります。

回路図のRL29の3pin、6pinにあたります。オシロの波形について、申し訳御座いませんが、

現在、測定基板が手元に無いため、すぐには波形を出せないです。TPA3112D1は「(2)OUTP-OUTNのショート」のショートも保護される仕様なのでしょうか。

Attachments:

ishi1126 様

回路図の情報をご提供下さり、ありがとうございます。

TPA3112D1は過電流を検出した際に/FAULTをLowにAssertしますので、

OUTP-OUTNをShortした際に過電流が流れるような条件に対しては

短絡保護が働きます。

OUTP-OUTNをShortした際、入力にはAudio Sourceや1kHzなどを

入力して検証を実施されたのでしょうか?Kato

> OUTP-OUTNをShortした際、入力にはAudio Sourceや1kHzなどを

> 入力して検証を実施されたのでしょうか?入力ソースはオーディオアナライザから1kHzを入力しています。

参考になるかわかりませんが、OUTP-OUTNのShort保護のためにPSW2(ポリスイッチ)を追加しており、

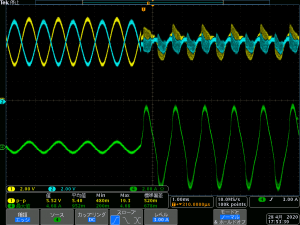

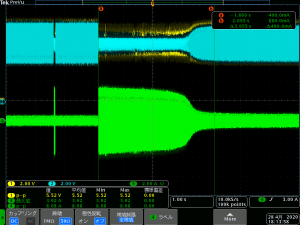

ポリスイッチの動作を確認した波形を添付致します。黄色と青色の波形がそれぞれOUTP、OUTNになります。

緑色の波形が電流波形です。OUTP-OUTNをShortした瞬間にp-pで9A程度の電流が流れます。

ポリスイッチが温まると電流は抑制されます。Attachments:

ishi1126 様

追加の波形情報をご提供下さり、ありがとうございます。

同様にOUTPを+12.5V、及びGNDにShortした際の波形もご提供頂くことは可能でしょうか?

正常にOvercurrent Protectionが機能していると思われるので、実測による過電流の閾値を

確認したいと考えております。Kato

ishi1126 様

追加でご確認頂きたいのですが、入力を1kHzから無信号にした際に

OUTP-OUTNをShortすると/FAULTはLowにAssertされますでしょうか?Kato

確認した所、以前GNDとのショートで/FAULTはLowにAssertされていたのですが、

別の基板で見るとGNDとのショートでも/FAULTがLowにAssertされなくなりました。Kato様の方で評価基板を使用したご確認をされているでしょうか。

評価基板と同じように回路図のL5、L6をフェライトビーズに変更して確認した所、

全ての短絡障害で/FAULTはLowにAssertされることを確認しました。ただし、フェライトビーズでは放射ノイズの影響が大きくなる懸念があり、

できればインダクタで進めたい状況です。EMC要求がかなり厳しい装置になります。以前にも常に/FAULTがLowにAssertされる問題でお問い合わせしていましたが、

今回は/FAULTがLowにAssertされない問題でした。

インダクタだと/FAULT機能が不安定になるように見受けられます。ishi1126 様

申し訳ございませんが、TPA3112D1EVMは保有しておらず、実機確認は行っておりません。

Inductor L5、L6をFerrite Beadsに変更することで、短絡試験時に/FAULTはLowに

Assertされるとのことですが、回路図上、/SDと/FAULTが直接接続されているため、

自動復帰を繰り返す動作になりますが、実機でもそのような動作でしょうか?また、ご使用のInductorの型番よりWebでSpecを確認致しましたが、直流重畳特性のDataがなく、

参考値として22uHと47uHで確認しますと、直流重畳許容電流が小さいようです。

例えば、直流重畳許容電流が大きい別のInductorでご確認頂くことは可能でしょうか?Kato

ご連絡頂き有難う御座います。

> Inductor L5、L6をFerrite Beadsに変更することで、短絡試験時に/FAULTはLowに

> Assertされるとのことですが、回路図上、/SDと/FAULTが直接接続されているため、

> 自動復帰を繰り返す動作になりますが、実機でもそのような動作でしょうか?はい。/SDと/FAULTは直接接続のため、自動復帰を繰り返します。

> また、ご使用のInductorの型番よりWebでSpecを確認致しましたが、直流重畳特性のDataがなく、

> 参考値として22uHと47uHで確認しますと、直流重畳許容電流が小さいようです。

> 例えば、直流重畳許容電流が大きい別のInductorでご確認頂くことは可能でしょうか?確認致します。何か進展があればまた連絡致します。

ishi1126 様

追加でご確認させて頂きたいのですが、Ferrite Beadsの型番をご教示頂けますと幸いです。

Kato

2020年6月1日 9:10 PMの確認で使用したフェライトビーズおよびコンデンサは以下になります。

フェライトビーズ:MPZ2012S101A (4A, 0.02Ω, 100Ω@100MHz)

コンデンサ:GRM1882C1H102JA01D (1nF)ishi1126 様

お忙しい中、Ferrite Beadsの型番をご教示下さり、ありがとうございます。

Inductorよりも定格電流が高いFerrite Beadsをご使用頂いているということを理解致しました。

Kato

インダクタ(DCR=312mΩ)を使用した回路で、

1. OUTP-GND または OUTN-GND 間のショートでは Fault が出る

2. OUTP-OUTN のショートでは Fault が出ない。

3. 基板の個体差により、1. の場合でも Fault が出ない物もあるまた、

4. フェライトビーズ(DCR=35mΩ)の場合は、全ての場合で Fault が正しく出る

5. EVM では DCR=87Ω のインダクタが指定されていて、おそらく全ての場合で正しく Fault が出る

という条件から判断すると、OUTP-OUTN 間の素子の直流抵抗の大きさが、過電流検出の可否に影響しているようです。TPA3112 内部の過電流検出は、OUTTP, OUTN 出力端子に直列に挿入された抵抗に生じる電圧降下で

判定していると予想します。

過電流検出を正常に動作させるには、出力端子に直列接続する外部素子の直流抵抗の最大値をどこまでにすればよいか、

教えていただけないでしょうか。

(予想では、OUTP, OUTN それぞれ 100mΩ 程度が上限値?)よろしくお願い致します。

ishi1126 様

原因調査に関する追加情報をご提供下さり、ありがとうございます。

InductorのDCRが大きいことが起因していると予想されているとのことですが、裏取りのために

Ferrite Beadsで短絡試験を行う際、定格電力の高い低抵抗を挿入して短絡して頂くことは可能でしょうか?

また、VCCやGNDに短絡した際に/FAULTがLowにAssertされる際の出力電流の実測値をご教示願います。念のための確認になりますが、短絡試験はSP_L1_OUT_DB1とSP_L2_OUT_DB1に対して実施されているという

認識ですが、正しいでしょうか?Kato

-

投稿者投稿

オーディオ

オーディオ