ホーム › フォーラム › Texas Instruments › クロック › HSYNCとクロックの関係

このトピックには4件の返信が含まれ、2人の参加者がいます。5 年、 2 ヶ月前に ![]() mtmt さんが最後の更新を行いました。

mtmt さんが最後の更新を行いました。

-

投稿者投稿

-

HSYNCとクロックの関係

デバイス型番:LMH1981;LMH1983LMH1981とLMH1983を使用したビデオシンクセパレータと、

クロック生成についてですが、

1)回路構成/条件

・LMH1981でシンクセパレートした、H_SYNC、V_SYNC、OE(ODD/EVEN)を

LMH1983に接続、LMH1983にて、TOF、148.35MHzを生成

・VIDEO入力フォーマット:1080i59.94、720P60等

・LMH1983のレジスタ設定に関しては、デフォルト値使用2)動作状況

・LMH1981からのH_SYNCの立下りをトリガに、

LMH1983が出力するCLKOUT3(PLL3_148.35MHz)を観測すると

クロックが揺れています。

・LMH1983の0x02(PLL Lock and Output Alignment Status)を

リードすると、PLL1~PLL4はLockしています。

・TOF3をトリガに、CLKOUT3(PLL3_148.35MHz)を観測すると、

TOF3とCLKは同期が取れているようです。3)質問

・H_SYNCと148.35MHzが同期が取れていないのは、

LMH1983の動作として、正常なのでしょうか。

・異常な場合に、考えられる原因は何でしょうか。

以上、宜しくお願い致します。okuiutosa様

ご連絡頂き、誠にありがとうございます。

■依頼事項1■

「LMH1983が出力するCLKOUT3(PLL3_148.35MHz)を観測するとクロックが揺れています。」

とございますが、こちらの波形取得を送付頂くことは可能でしょうか?

また、波形に関してはオシロの重ね書きで線が太く見えるような形でしょうか?■依頼事項2■

CLK3の出力に関しては、データシート記載が分かりにくいかもしれませんが、

下記手順でレジスタ設定を実行することにより、 PLL3 CLK出力のDuty崩れを防止(初期化)が可能になります。

こちらのレジスタ設定も一度確認頂けますでしょうか?

1.Power Up

2.ソフトウェアリセット ADDR 0x05 [7] = 1

3. クロスポイントスイッチの設定変更

ADDR 0x09 [3:0] = 0010’b

ADDR 0x09 [3:0] = 0000’b

4.PLL1をFree Run Modeに設定

REG 0x05 [4:3] = 00’b //PLL1 : Free Run mode

5. TOF3のAlignment Mode設定変更

初期値 -> Always Align -> Wait -> 初期値(Never Align)

ADDR 0x13 [5:4] = 10’b //TOF3 : Always Align

Wait 500ms (More than 2 output frame period)

ADDR 0x13 [5:4] = 11’b // TOF3 : Never Alignまた、波形等に関してコンフィデンシャルなことを含む場合、直接やり取りさせて頂くことも可能と存じます。

弊社の営業から連絡させていただければと存じます。以上、よろしくお願いいたします。

mtmt

ご担当者様

波形ですが、クロックが定まらない様な形です。

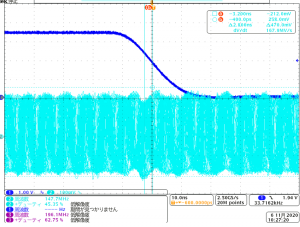

Fig1 CH1:HSYNC、CH2:PLL3_CLKOUT(148.35MHz)トリガ条件HSYNC

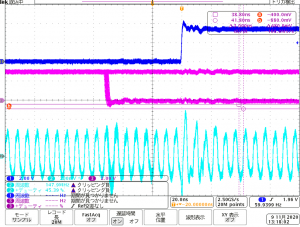

Fig2 CH1:TOF3、CH2:PLL3_CLKOUT(148.35MHz)、CH3:HSYNC トリガ条件TOF3となります。

レジスタ設定に関し、確認致しますが、使用方法はGENLOCKとなりますが、

前述の初期化後、GENLOCKに戻すということで宜しいでしょうか。以上、宜しくお願い致します。

Attachments:

okuiutosa様

■頂いた波形からの考察■

頂いた波形から、1080p59.9の場合、HSYNCをトリガに148.35MHzクロックを観測すると、

流れてはいないがクロックの遷移タイミングが一定の範囲で、前後にずれていると推測します。

ジッタが観測されていると思います。予期される結果です。

LMH1983は入力ビデオに含まれる低周波ジッタを除去した後、148.35MHzクロックを生成するので、両者の間には、除去した分のジッタが観測されます。一方、720p60をリファレンスとした場合、HSYNCをトリガに148.35MHzクロックを観測すると、波形は流れます。なぜなら、720p60と整数関係にあるクロックは148.5MHzクロックで、148.35MHzクロックは1/1.001ずれます。オシロで観測すると流れます。

720p59.9を入力にすると、1080p59.9の時と同じ結果になるはずです。■追加質問■

レジスタ設定に関し、確認致しますが、使用方法はGENLOCKとなりますが、

前述の初期化後、GENLOCKに戻すということで宜しいでしょうか。■回答■

その御認識で問題ございません。「5.」の内容の後、Free Run Modeから御使用のGENLOCKにお戻しいただければ幸いです。さらに詳細な内容に関しましては御購入先の代理店様から確認頂けますと幸いです。

またE2Eという英語ですが質問可能なフォーラムもございますので、こちらも併せてご検討いただければ幸いです。以上、よろしくお願いいたします。

mtmt

-

投稿者投稿

クロック

クロック