ホーム › フォーラム › Texas Instruments › データコンバーター › DAC update wait timeについて

このトピックには29件の返信が含まれ、2人の参加者がいます。5 年、 2 ヶ月前に Nishie さんが最後の更新を行いました。

-

投稿者投稿

-

DAC update wait timeについて

デバイス型番:DAC81408DAC81408のデータシートにされております

Sequential DAC update wait timeと、Broadcast DAC update wait timeは、

何の時間か教えて下さい。

Data Registerにデータを設定してから、次にData Registerにデータを設定するまでの

必要なwait時間でしょうか?maida様

お問い合わせ頂きありがとうございます。

Sequential DAC update wait timeは、CH毎にデータ書き込みを行う際の待機時間になります。

つまり、あるCHのデータレジスタに書き込みを行ってから、他のCHのデータレジスタに書き込みを行う場合の待機時間になります。

一方でBroadcast DAC update wait timeは、Broadcast modeにてデータ書き込みを行う際の待機時間になります。

Broadcast Registerにより1つのデータをレジスタに書き込み、複数のDACからそのデータを出力し、新たにデータを書き込みしたい場合の待機時間になります。

以上、宜しくお願いいたします。

Nishie

ご回答ありがとうございました。

念のため確認させてください。

DAC81408でCH1→CH3→CH5→CH7の順にSPIでDATAを設定しようとしております。

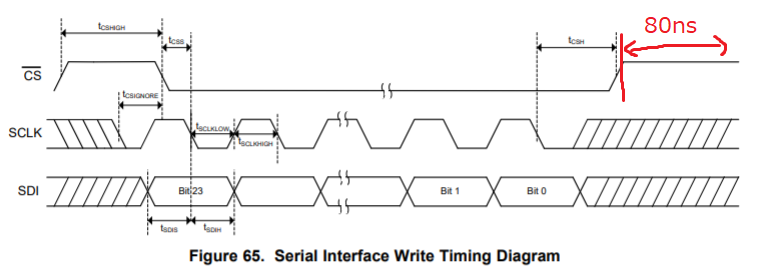

CH1のデータを設定した後にCH3のデータを設定するまでのCSをHighにする時間を、

tCSHIGHを参考に80nsにしようとしておりましたが、

Sequential DAC update wait timeより、CH1のデータを設定した後にCH3のデータを

設定するまでのCSをHighにする時間は2.4us以上必要でしょうか?maida様

CH1のデータ設定後、CH3のデータ設定を行う場合は、2.4us以上CSをHighにして頂く必要がございます。

以上、宜しくお願いいたします。

Nishie

ご回答ありがとうございました。

追加で質問です。

SYNCCONFIG Register(Offset = 06h)でsynchronous modeとasynchronous modeを選択できますが、

synchronous modeとasynchronous modeのどちらのモードでも

CH1のデータ設定後にCH3のデータ設定を行うまで、CSを2.4us以上Highにする必要がございますでしょうか?・現在弊社では電源起動後の初期設定として以下の様にレジスタ設定を行っていますが、

以下のレジスタ設定の中で、CS High時間2.4usにWaitが必要なレジスタはどこになりますか?1.アドレス0x03に0x0A04 // device power-down mode解除

2.アドレス0x0Bに0xAAAA // OUT7-4 ±10V設定

3.アドレス0x0Cに0xAAAA // OUT3-0 ±10V設定

4.アドレス0x06に0x0FF0 // LDAC trigger (synchronous mode)

5.アドレス0x14に0x8000 // OUT0 0V

6.アドレス0x15に0x8000 // OUT1 0V

7.アドレス0x16に0x8000 // OUT2 0V

8.アドレス0x17に0x8000 // OUT3 0V

9.アドレス0x18に0x8000 // OUT4 0V

10.アドレス0x19に0x8000 // OUT5 0V

11.アドレス0x1Aに0x8000 // OUT6 0V

12.アドレス0x1Bに0x8000 // OUT7 0V

13.アドレス0x0Eに0x0010 // register LDAC

14.アドレス0x09に0xF00F // power-down mode解除・上記初期設定後は、使用するDACnレジスタ(0x14~0x1B番地)のみ設定し

LDAC端子制御にて同時に設定値を反映するような使用方法としております。

この様なLDAC端子制御に同期したDAC出力更新の場合でもDACnレジスタの

CS High時間2.4usは必要となるのでしょうか?-

この返信は5 年、 3 ヶ月前に

maida さんが編集しました。

maida様

ご連絡が遅くなり、申し訳ございません。

現在、メーカーに確認しておりますので、もう少々お待ち頂けますと幸いです。

またmaida様の使用方法として、データ更新を早くしたいという認識でよろしいでしょうか。

以上、何卒宜しくお願いいたします。

Nishie

メーカーへの確認お手数をお掛けしますが宜しくお願いします。

データ更新を早くしたいという認識で合っておりますが、

データ更新に必要なWaitがございましたら、教えて頂きたいと思っているところです。maida様

ご回答頂き、ありがとうございます。

その点もふまえて確認できればと存じます。

以上、宜しくお願いいたします。

Nishie

maida様

ご回答が遅くなり申し訳ございません。

■synchronous modeとasynchronous modeのどちらのモードでも、CH1のデータ設定後にCH3のデータ設定を行うまで、CSを2.4us以上Highにする必要がございますでしょうか?

→どちらのmodeも2.4us以上、CSをHighにする必要がございます。

Asynchronous modeの場合、CH1設定後からCH3の設定を開始するまでの待ち時間(2.4us)は必要ですが、1つのCHに対するデータの反映に待ち時間はございません。

■以下のレジスタ設定の中で、CS High時間2.4usにWaitが必要なレジスタはどこになりますか?

→すべてのレジスタ設定に2.4us以上の待ち時間が必要となります。

■LDAC端子制御に同期したDAC出力更新の場合でもDACnレジスタのCS High時間2.4usは必要となるのでしょうか?

→LDACによる制御(Synchronous mode)を行った場合も、2.4us以上必要となります。

本デバイスにはStreaming modeがございまして、こちらを使用した場合、連続した8つのDAC CHのレジスタ更新を待ち時間なく行うことが可能です。

ただしCH1→CH2→CH3というように連続して更新を行いますので、CH1→CH3というような更新方法ができなくなってしまいます。

以上、宜しくお願いいたします。

Nishie

ご連絡しましたレジスタ設定に対し、すべてのレジスタ設定に2.4us以上の待ち時間が必要とのご回答に納得いかない点があり追加で質問します。

データシートではCS hight時間は最小25nsとなっております。

こちらの使用環境ではCS High時間は80nsで使用しておりますが、

初期設定時には一部出力電圧が反映されないと言った現象が100%発生するものの

通常動作のLDAC更新動作では事前にDACデータレジスタをCS High時間80nsで

アクセスしても現時点では100%出力電圧に反映されるため、CS High時間に2.4usが必要と言う訳では無く、

ご連絡しました初期設定時のレジスタ設定順番の中のどこかに『Sequential DAC update wait time』

2.4usに該当する時間が必要だと考えておりますが如何でしょうか?なお、以下にデータシートの記載を抜粋すると

・DACデータレジスタに書き込まれたデータは、最初はDACバッファレジスタに格納されます。

・DACバッファレジスタからDACアクティブレジスタへのデータの転送は、即時発生する【非同期モード】、

またはDACトリガー信号によって開始される【同期モード】構成ができます。

・DACアクティブレジスタが更新されると、DAC出力は新しい値に変更されます。

・どちらの更新モードでも、DAC出力の更新の間に1 µsの最小待機時間が必要です。と記載されており、『Sequential DAC update wait time』の対象となる時間は

【Figure 47. DACx1408 DAC Block Diagram】のデータフローの内、

DACアクティブレジスタからDAC出力に対する更新が対象では無いかと

考えておりますが、如何でしょうか?-

この返信は5 年、 3 ヶ月前に

maida さんが編集しました。

maida様

レジスタ設定に関して、データシートから読み取ることが出来ない為、詳細を確認したうえでメーカーに問い合わせをしたいと考えております。

80nsで設定できているレジスタアドレスと書き込んでいるデータの詳細をご教授頂けないでしょうか。

またTdacwaitに関して、メーカーに確認中ですのでもう少々お時間を頂けますと幸いです。

以上、宜しくお願いいたします。

Nishie

80nsで設定できているレジスタアドレスは下記のとおりです。

#14023でご連絡しました初期設定後、下記のアクセスをしております。1.アドレス0x14(or 0x15)に16bitのデータを設定

2.アドレス0x16(or 0x17)に16bitのデータを設定

3.アドレス0x18(or 0x19)に16bitのデータを設定

4.アドレス0x1A(or 0x1B)に16bitのデータを設定

5.LDACpinを20ns Low

1と2,2と3,3と4のSPIのアクセスのCS High時間の間隔を80nsに設定しております。maida様

ご連絡ありがとうございます。

1, 2, 3, 4において「データを設定」と記載されておりますが、

このデータの設定はbit0までWriteを行い、Tcshも経過したタイミングという認識でよろしいでしょうか。

また、CS Highの開始タイミングは以下の画像の赤文字の通りでよろしかったでしょうか。

以上、宜しくお願いいたします。

Nishie

データの設定はbit0までWriteを行い、Tcshも経過したタイミングという認識で合ってます。

また、CS Highの開始タイミングは頂いた画像の赤文字の通りでよろしいです。 -

この返信は5 年、 3 ヶ月前に

-

投稿者投稿

データコンバーター

データコンバーター