ホーム › フォーラム › Texas Instruments › データコンバーター › DAC update wait timeについて

このトピックには29件の返信が含まれ、2人の参加者がいます。5 年、 2 ヶ月前に Nishie さんが最後の更新を行いました。

-

投稿者投稿

-

maida様

お待たせして申し訳ございません。

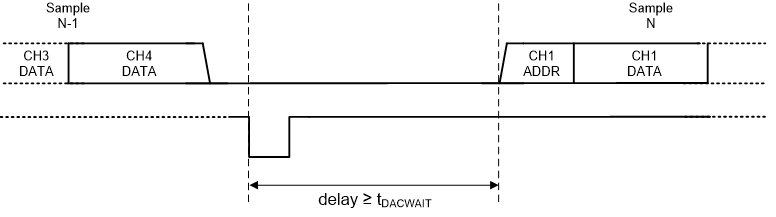

TdacwaitはSynchronous modeの場合、LDACの立下りエッジから後続のLDACの立下りエッジまでの待機時間となります。

下の図の2番目の波形がLDACになります。

また、レジスタ設定において

5.LDACpinを20ns Low

から再度

1.アドレス0x14(or 0x15)に16bitのデータを設定

を行うまでの間に待機時間はどのくらい設けておりますでしょうか。

10.3.1.2.1 DAC Register Synchronous and Asynchronous Updatesの最後の行に記載されている「In both update modes a minimum wait time of 1 µs is required between DAC output updates.」につきまして、1us は 2.4usの誤記となります。

以上、宜しくお願いいたします。

Nishie

ご回答ありがとうございました。

Synchronous modeの場合、Tdacwaitは、LDACの立下りエッジから後続のLDACの立下りエッジまでの待機時間とのとこで承知しました。

現状、LDACpinを20ns Lowから再度アドレス0x14(or 0x15)に16bitのデータを設定を行うまでの間に待機時間は、25us程度を想定しています。確認になりますが、頂いたタイムチャートのCH3 DATAレジスタにアクセスしてから、CH3 DATAレジスタにアクセスするまでに必要なCSのwait時間は、データシートに記載されておりますtcshighの25ns以上で宜しいでしょうか?

また、#14023項の質問の繰り返しになりますが、電源起動後DAC81408に初期設定として以下の様にレジスタ設定を行っていますが、レジスタ間のアクセスのwait時間を80nsとしたところうまくいきません。

1.アドレス0x03に0x0A04 // device power-down mode解除

2.アドレス0x0Bに0xAAAA // OUT7-4 ±10V設定

3.アドレス0x0Cに0xAAAA // OUT3-0 ±10V設定

4.アドレス0x06に0x0FF0 // LDAC trigger (synchronous mode)

5.アドレス0x14に0x8000 // OUT0 0V

6.アドレス0x15に0x8000 // OUT1 0V

7.アドレス0x16に0x8000 // OUT2 0V

8.アドレス0x17に0x8000 // OUT3 0V

9.アドレス0x18に0x8000 // OUT4 0V

10.アドレス0x19に0x8000 // OUT5 0V

11.アドレス0x1Aに0x8000 // OUT6 0V

12.アドレス0x1Bに0x8000 // OUT7 0V

13.アドレス0x0Eに0x0010 // register LDAC

14.アドレス0x09に0xF00F // power-down mode解除

レジスタアクセスの間で、CS High時間を80usよりも長く設定する必要があるところがございませんでしょうか?

5から12までのDATAレジスタ同士のアクセスの間隔に25ns以上のCSのwait時間が必要とすると、DATAレジスタ同士以外の1から2,2から3,3から4,4から5,12から13,13から14のレジスタのアクセス間隔で、CS High時間を80usよりも長く設定する必要があるところがございませんでしょうか?maida様

■LDACの立ち下りエッジから再度アドレス0x14(or 0x15)に16bitのデータを設定を行う(CSの立ち上がりエッジ)までの待機時間だと認識しておりますが、Synchronous mode時に、この時間を2.4us以上に設定して頂くことでデータシートの規定内での動作となります。

また5(LDACの立ち下がりエッジ)から再度5(LDACの立ち下がりエッジ)の間隔を2.4us以上に設定して頂く事でもデータシートの規定内になると存じます。

■タイムチャートのSample N-1はStreaming modeでの動作となるため、CH3とCH4の間にCS Highの時間はございません。

■申し訳ございません。

初期設定時の待機時間について、まだ明確な事が分かっていない為、分かり次第ご連絡できればと存じます。

年末のため回答にお時間がかかってしまう可能性がございます。ご了承ください。

以上、宜しくお願いいたします。

Nishie

maida様

#14060にて「初期設定時には一部出力電圧が反映されないと言った現象が100%発生するものの」と記載されておりますが、どのCHにどんな異常が発生しているのか詳細をご教授頂けないでしょうか。

また異常が発生したCHのレジスタデータをフィードバックして頂けないでしょうか。

初期設定時のレジスタアドレスの順番やWait時間に問題がないかについては、現在メーカーに確認中です。

申し訳ございません。

考えられる原因としてClock等にノイズが入っておりシリアルデータが正確に反映されていない可能性がございます。

以上、宜しくお願いいたします。

Nishie

> どのCHにどんな異常が発生しているのか詳細をご教授頂けないでしょうか。

OUT0-7に0Vを出力するため、アドレス0x14-1Bに0x8000を設定したところ、

OUT1,3,5,7に-10Vや-5Vが出力します。>また異常が発生したCHのレジスタデータをフィードバックして頂けないでしょうか。

DACのレジスタをreadして確認してほしいとの意味でしょうか?

もしそうでしたら、設計した基板ではSDO接続していないため確認できません。>考えられる原因としてClock等にノイズが入っておりシリアルデータが正確に反映されていない可能性がございます。

レジスタのアクセス間隔を長くすると、OUT1,3,5,7の出力も期待した0Vになる為、

ノイズは関係ないと思っております。

初期設定時のレジスタアドレスの順番やWait時間に問題がないかについて、回答をお待ちしております。-

この返信は5 年、 2 ヶ月前に

maida さんが編集しました。

maida様

ご回答頂きありがとうございます。

・OUT1, 3, 5,7で負の出力電圧(-10Vと-5V)が発生しているとのこと承知いたしました。

正の出力電圧になることはないという認識でよろしかったでしょうか。

・ご認識の通り、DACレジスタをReadして確認して頂きたかったのですが、SDO接続しておらず値が読み出せないとのこと承知いたしました。

・アクセス間隔を長くしたとありますが、具体的にどの間隔をどの長さに変更したのかご教授頂けないでしょうか。

以上、宜しくお願いいたします。

Nishie

>正の出力電圧になることはないという認識でよろしかったでしょうか。

はいそうです。ちなみにOUT0,2,4,6は0Vが出力します。>アクセス間隔を長くしたとありますが、具体的にどの間隔をどの長さに変更したのかご教授頂けないでしょうか。

全レジスタのアクセスの間隔を3usに設定しました。maida様

回答が遅くなってしまい申し訳ございません。

セッティングレジスタ(0x02h~0x0Eh)設定後のCS Highの時間は最低50ns設けて頂ければ問題ございません。

セッティングレジスタ以外のレジスタ設定に関しては、レジスタ設定後、2.4us以上待機時間を設けて頂きますようお願いいたします。

以上、宜しくお願いいたします。

Nishie

レジスタアクセス後ののCS Highの時間の確認有難うございます。

セッティングレジスタ(0x02h~0x0Eh)設定後のCS Highの時間は最低50ns、セッティングレジスタ以外のレジスタ設定に関しては、レジスタ設定後、2.4us以上待機時間を設けるよう回答頂きましたが、下記の初期設定の場合、1,2,3,4,13,14のレジスタアクセス後のCS Highの時間は最低50nsで、5~12のデータレジスタアクセス後のCS Highの時間は2.4us必要ということでしょうか?

もし、データレジスタアクセス後のCS Highの時間が2.4us必要ということでしたら、下記のDAC出力更新の設定でCS Highの時間を80nsで設定してもデータ更新ができていることと矛盾しております。再度確認させてください。

連絡しました初期設定のレジスタの設定の順番に問題ございませんでしょうか?

セッティングレジスタ(0x02h~0x0Eh)によっては、設定後のCS Highの時間が50nsよりも長い時間必要なレジスタがございませんでしょうか?

データレジスタアクセス後のCS Highの時間が2.4us必要なのでしょうか?■初期設定

1.アドレス0x03に0x0A04 // device power-down mode解除

2.アドレス0x0Bに0xAAAA // OUT7-4 ±10V設定

3.アドレス0x0Cに0xAAAA // OUT3-0 ±10V設定

4.アドレス0x06に0x0FF0 // LDAC trigger (synchronous mode)

5.アドレス0x14に0x8000 // OUT0 0V

6.アドレス0x15に0x8000 // OUT1 0V

7.アドレス0x16に0x8000 // OUT2 0V

8.アドレス0x17に0x8000 // OUT3 0V

9.アドレス0x18に0x8000 // OUT4 0V

10.アドレス0x19に0x8000 // OUT5 0V

11.アドレス0x1Aに0x8000 // OUT6 0V

12.アドレス0x1Bに0x8000 // OUT7 0V

13.アドレス0x0Eに0x0010 // register LDAC

14.アドレス0x09に0xF00F // power-down mode解除■DAC出力更新

初期設定後、下記の1~5の順番で設定しDACの出力を更新しております。

1.アドレス0x14(or 0x15)に16bitのデータを設定

2.アドレス0x16(or 0x17)に16bitのデータを設定

3.アドレス0x18(or 0x19)に16bitのデータを設定

4.アドレス0x1A(or 0x1B)に16bitのデータを設定

5.LDACpinを20ns Low

1~4のレジスタアクセスのCS High時間は80nsに設定。maida様

大変申し訳ございません。

継続して、メーカーへ以下の内容で確認を行っているのですが回答が得られていない状況です。

1. 初期設定、DAC更新の方法に問題がないかどうか

2. 初期設定時、データレジスタ間のCS Highの時間が50nsか2.4usかどうか

3. DAC更新時、CS Highが80nsで動いているが問題ないかどうか

以上、宜しくお願いいたします。

Nishie

maida様

大変お待たせいたしました。

・初期設定時、1~13までのCS Highの時間は50ns以上設けて下さい。

13~14の間にLDACをLowにした後、DACレジスタ更新のため2.4us(Tdacwait)以上待機時間を設けて下さい。

また、レジスタアドレス0x03hのデフォルト設定は0x0A24になります。

・DAC出力更新において、1~5までのCS Highの時間は50ns以上設けて下さい。

5でLDACをLowにした後、DACレジスタ更新のため待機時間を2.4us(Tdacwait)以上設けて下さい。

以上、宜しくお願いいたします。

Nishie

ご回答ありがとうございます。

追加で質問します。>13~14の間にLDACをLowにした後、DACレジスタ更新のため2.4us(Tdacwait)以上待機時間を設けて下さい。

13でTRIGGER Register(0x0E)に0x0010をwriteして更新しようとしており、その場合LDACpinをLOWにする必要はないとの認識で合ってますでしょうか?

また、13~14の間に2.4us(Tdacwait)以上の待機時間が必要ということでしょうか?>また、レジスタアドレス0x03hのデフォルト設定は0x0A24になります。

SPICONFIG Register(0x03)の初期値が0x0A24ですが、power-down modeからacitve modeにする為、1でSPICONFIG Register(0x03)に0x0A04を設定しておりますが、問題がございましたら教えて下さい。maida様

■13でTRIGGER Register(0x0E)に0x0010をwriteして更新しようとしており、その場合LDACpinをLOWにする必要はないとの認識で合ってますでしょうか?

また、13~14の間に2.4us(Tdacwait)以上の待機時間が必要ということでしょうか?

→ご認識の通り、TRIGGER Registerに0x0010を書き込んで頂ければ、LDACピンをLowにする必要はございません。

はい、13~14の間に2.4us以上待機時間を設けて下さい。

■SPICONFIG Register(0x03)の初期値が0x0A24ですが、power-down modeからacitve modeにする為、1でSPICONFIG Register(0x03)に0x0A04を設定しておりますが、問題がございましたら教えて下さい

→問題ございません。

以上、宜しくお願いいたします。

Nishie

ご回答ありがとうございました。

参考の為教えて下さい。

DAC81408を使用する場合、リセット解除後DACの出力等を初期設定すると思いますが、アドレス0x09でしpower downを解除するタイミングについて、お奨めのタイミングがございましたら教えて下さい。

連絡しております初期設定のように、例えばアドレス0x14-0x1Bのデータレジスタにデータを設定後、アドレス0x09に0xF00Fを設定しpower downを解除する手順が宜しいでしょうか?maida様

現在の初期設定の手順で問題ございません。

タイミングとしてはレジスタアドレス0x0Eh設定時にDACの更新を行っておりますので、2.4us以上待機時間を設けた後にレジスタアドレス0x09hにてPower-down modeを解除して頂ければと存じます。

以上、宜しくお願いいたします。

Nishie

-

この返信は5 年、 2 ヶ月前に

-

投稿者投稿

データコンバーター

データコンバーター