ホーム › フォーラム › Texas Instruments › マイコン › C2000 › PLL機能のデバッグ(DCCモジュール)

このトピックには4件の返信が含まれ、2人の参加者がいます。5 年、 1 ヶ月前に ![]() Ge さんが最後の更新を行いました。

Ge さんが最後の更新を行いました。

-

投稿者投稿

-

PLL機能のデバッグ(DCCモジュール)

デバイス型番:F280049お世話になります。

F280049マイコンにて、以下の設定にて100MHzのシステムクロックを実現しようとしています。

OSCCLK: 10MHz

SYSPLLMULT.IMULT: 40

SYSPLLMULT.FMULT:0

SYSPLLMULT.ODIV: 1 (/2)

SYSCLKDIVSEL.PLLSYSCLKDIV: 1 (/2)各レジスタ設定後、XCLKOUTから

PLLSYSCLKやPLLRAWCLKを出力し実測したところ、

正常に設定したクロックで動作している様なのですが、

C2000Wareのf28004x_sysctrl.cからIsPLLValid()を使用して

確認すると戻り値が0となり、DCCモジュールでのチェックは失敗しているようです。IsPLLValidの引数はそれぞれ以下の通りです。

oscSource = 1;

imult = 40;

fmult = 0;これについてデバッグしたいのですが、Dcc0Regs内を確認しようとすると

「Memory map prevented reading」となっており確認することが出来ません。上記現象について、デバッグを進めるためにどの様にすれば良いでしょうか。

お問い合わせありがとうございます。

Dcc0Regs内の値が確認できないとのことなので、CCS側の問題である可能性がございますので、最新のCCSを使用し、動作検証をお願いできますでしょうか。

https://software-dl.ti.com/ccs/esd/documents/ccs_downloads.html尚、私のPCにはCCSv10.1をインストールしておりますが、こちらのバージョンではDcc0Regsの値を確認することができました。

また、F28004xのPLLにはErrataがございますので、Errata資料のワークアラウンドに記載のSysCtl_setClock()を使用しクロック設定をお願い致します。

TMS320F28004x MCUs Silicon Errata

https://www.tij.co.jp/jp/lit/pdf/sprz439

(p.17) PLL: PLL May Not Lock on the First Lock AttemptSysCtl_setClock()は、C2000wareのdriverlib内の関数となります。

また不明点が御座いましたらお問い合わせください。

以上、よろしくお願いいたします。

ご回答ありがとうございます。

CCSを最新版にすることによって、Dcc0Regs内の値が確認できるようになりました。

PLLの設定についてはMathworks社のライブラリを使用しているのですが、

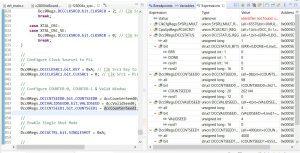

PLLのLockは100回まで試行する設定になっているので問題ないかと存じます。IsValidPLL()実行時の動作を確認すると、以下の場所でレジスタの値が異常であるようです。

—(略)—

// Clear Error & Done Flag

//

Dcc0Regs.DCCSTATUS.bit.ERR = 1; //Dcc0Regs.DCCSTATUS.allは1になるが、~.ERRは0のまま

Dcc0Regs.DCCSTATUS.bit.DONE = 1; //同上

—(略)—

// Configure COUNTER-0, COUNTER-1 & Valid Window

//

Dcc0Regs.DCCCNTSEED0.bit.COUNTSEED0 = dccCounterSeed0; // 代入値は98, Dcc0Regs.DCCCNTSEED0.allが98, ~.COUNTSEED0は262144(0x40000)

Dcc0Regs.DCCVALIDSEED0.bit.VALIDSEED = dccValidSeed0; // 代入値、~.all, =.VALIDSEED すべて4

Dcc0Regs.DCCCNTSEED1.bit.COUNTSEED1 = dccCounterSeed1; // 代入値は4000, ~.allは4000, ~.COUNTSEED1は65536(0x10000)// Enable Single Shot Mode

//

Dcc0Regs.DCCGCTRL.bit.SINGLESHOT = 0xA; //実行後の値が0—(略)—

// Wait until Error or Done Flag is generated

//

while((Dcc0Regs.DCCSTATUS.all & 3) == 0){} //.EERORも.DONEも0だが、~.allが1なので即抜けるAttachments:

ご連絡ありがとうございます。

PLLの設定について、Mathworks社のライブラリを使用しているとのことですが、こちらのライブラリを見ると、TI社から提供されているC2000wareのソースコードをベースに作成されたもののようです。

古いC2000wareのF28004x向けのPLL設定コードには不具合があったため、Mathworks社のライブラリが旧バージョンのPLL設定コードをベースに作成されている場合には、IsValidPLL()でエラーが発生してしまいます。お手数ではございますが、以下のリンクより最新のC2000wareをインストールしていただき、以下のフォルダのプロジェクトをインポートして再度動作テストをしていただけますでしょうか。

~ti\c2000\C2000Ware_xxxx9\device_support\f28004x\examples\ledC2000WARE

https://www.tij.co.jp/tool/jp/C2000WARE上記のサンプルで問題が発生しない場合には、Mathworks社のライブラリのコードと比較し調査をお願い致します。

ご連絡ありがとうございます。

C2000Ware 3.00.00のサンプルコードからは問題が発生しませんでした。

また、Mathworksライブラリの使用時において、ODIV = 1(SYSPLLMULT.ODIV = 0)以外となる設定の際に

同現象が発生することの再現がとれましたので、Mathworksサポートに調査依頼を致しました。ご対応ありがとうございました。

ご連絡ありがとうございます。現象の再現ができたとのことで安心いたしました。

また不明点が御座いましたらお問い合わせください。以上、今後とも宜しくお願いいたします。

-

投稿者投稿

C2000

C2000