ホーム › フォーラム › Texas Instruments › マイコン › C2000 › ePWMのハイレゾモードが適用されない

-

投稿者投稿

-

ePWMのハイレゾモードが適用されない

デバイス型番:320F28075お世話になります。

早速ですが、

今まで、相補モードでPWMAにハイレゾを適用してうまく動作していました。

しかし、プッシュブル出力を得るために、CMPA、CMPBを使用してPWMA、Bを生成しています。

そこに、今回PWMA,Bにそれぞれハイレゾを適用しようと思いますが、設定を変えても変化はありません。

何か関連したレジスタ設定があるのでしょうか、ちなみに添付したファイルは

C:\ti\controlSUITE\device_support\F2807x\v210\F2807x_examples_Cpu1\hrpwm_duty_sfo_v8\cpu01

を私の環境と同じく60KHzのePWM4のみアップダウンカウント ピリオド 500に変更していますが正しく動作しています。

しかしながら、当方の開発中のプログラムにePWM4の設定を全て合わせてもハイレゾは適用されません。

なにが考えられるでしょうか、宜しくお願いします。

Attachments:

解決しました。

古い SFO_v8_fpu_lib_build_c28.lib をリンクしていたこと、

また、SFO() のトレーニング方法が以前と異なるようで、

サンプルに合わせたところハイレゾ部分が信号に付加されるようになりました。//

// Calling SFO() updates the HRMSTEP register with calibrated MEP_ScaleFactor.

// HRMSTEP must be populated with a scale factor value prior to enabling

// high resolution period control.

//

while(status == SFO_INCOMPLETE)

{

status = SFO();

if(status == SFO_ERROR)

{

error(); // SFO function returns 2 if an error occurs & # of MEP

} // steps/coarse step exceeds maximum of 255.

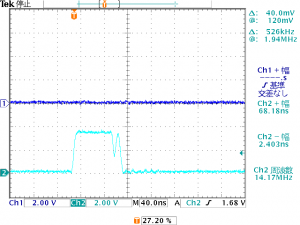

}信号波形を見ると付加された部分とメインのPWMパルスとの間にグリッジが発生していますが回避方法はありますか、

Attachments:

失礼しました。

All ePWM modules operating in HRPWM incur only a 3-SYSCLKOUT cycle minimum duty cycle

limitation when high-resolution period control is not used. If high-resolution period control is enabled,

there is an additional duty cycle limitation 3-SYSCLKOUT cycles before the end of the PWM periodmickey.mouse様

お世話になっております。

>信号波形を見ると付加された部分とメインのPWMパルスとの間にグリッジが発生していますが回避方法はありますか、

→頂いている波形のようなグリッチはサンプルコードをそのまま動作させた場合も発生しますでしょうか?

また、こちらは貴社のカスタム基板で動作させているという認識で合っておりますでしょうか?

また、下記内容を記載いただいている意図が理解できませんでしたが、詳細をご教示いただけませんでしょうか。

All ePWM modules operating in HRPWM incur only a 3-SYSCLKOUT cycle minimum duty cycle

limitation when high-resolution period control is not used. If high-resolution period control is enabled,

there is an additional duty cycle limitation 3-SYSCLKOUT cycles before the end of the PWM period以上、よろしくお願いいたします。

uchidaK

グリッジの件は削除させていただきます。サンプルコードでは発生しません。別のコード同等の初期化をしていますが、ブレークして小数点以下をデバッガのレジスタ変更で行ったいました。その過程で間違えた値をどこかに違った値を書き込んでしまったのかもしれません。そのときは実数部分が3より大きければ方形波になっていましたので英文を添付しました。

基板は、弊社オリジナルです。mickey.mouse様

お世話になっております。

ご質問は取り下げるとのことで承知いたしました。

本スレッドはクローズさせていただきます。

また何かございましたら、新規で投稿いただければと思いますので、

よろしくお願いいたします。

uchidaK

-

投稿者投稿

C2000

C2000