ホーム › フォーラム › Texas Instruments › 電源IC › TPS65986のイレギュラー時動作について

このトピックには5件の返信が含まれ、2人の参加者がいます。7 年、 8 ヶ月前に ![]() KJ さんが最後の更新を行いました。

KJ さんが最後の更新を行いました。

-

投稿者投稿

-

TPS65986のイレギュラー時動作について

デバイス型番:TPS65986TPS65986に関しまして以下の動作時の詳細をご教示頂きたいと思います。

・過電流制限機能について

データシートの「8.3.3.4 PP_5V0 Current Limit」項目等に過電流時の制御情報が記載されていますが、過電流状態が解除された際には、通常動作に自動的に戻るのでしょうか?またはリセット等をかけないと過電流制限状態を維持し続けるのでしょうか?

・SPIフラッシュ未検出時動作について

TPS65986に電源が投入されて外部SPIフラッシュが検出できなかった場合はデータシートの「8.4.7 Invalid Flash Memory」に記載されているようにVBUSが投入されているか、デバイスが接続されているかをチェックし続ける挙動をすると理解していますが、その間各端子はPin Funcitonsに記載されているPOR STATE状態を維持し続けるという認識でよろしいでしょうか?

以上、宜しくお願い致します。

nakagawa様

ご質問以下回答致します。

・過電流制限機能について

過電流状態が解除された際には自動的に通常動作に復帰します。・SPIフラッシュ未検出時動作について

はい、ご認識の通り、POR STATE状態を維持します。以上、宜しくお願い致します。

KJKJ様

ご回答ありがとうございます。

>過電流状態が解除された際には自動的に通常動作に復帰します。

上記ご回答頂きましたが、過電流時の監視の挙動(どのような周期で過電流確認をして、どのような条件で過電流状態解除と判断しているか等)に関して詳細な資料があれば頂けますでしょうか?以上、宜しくお願い致します。

nakagawa様

過電流状態に入った際の挙動については、データシートのP.39,40を参照ください。

また、過電流状態については、0x1Aレジスタの16bitのステータスを読むことで判ります。

詳細については以下のTechnical Reference Manualをご確認ください。

http://www.ti.com/lit/ug/slvuan1a/slvuan1a.pdf

以上、宜しくお願い致します。

KJ様

ご回答ありがとうございます。

>過電流状態に入った際の挙動については、データシートのP.39,40を参照ください。

>また、過電流状態については、0x1Aレジスタの16bitのステータスを読むことで判ります。上記情報では過電流発生時の状態確認を出来ますが、過電流状態が解除された際の挙動の記載は見られませんでした。

「controlled automatically by the digital core」と記載されているので自動的に過電流検出をデジタルコアが検出するのだと

理解しておりますが、以下の点を懸念しており、過電流保護解除時の動作をご教示頂ければと思います。・過電流解除の解除を周期的に保護状態を解除して、問題なければ通常動作に戻り、過電流状態が続いていれば再度保護状態に入れるといった挙動(hiccupモード)を行っていた場合、確認周期が早すぎた場合にノイズ原因等にならないか。

以上、宜しくお願い致します。

nakagawa様

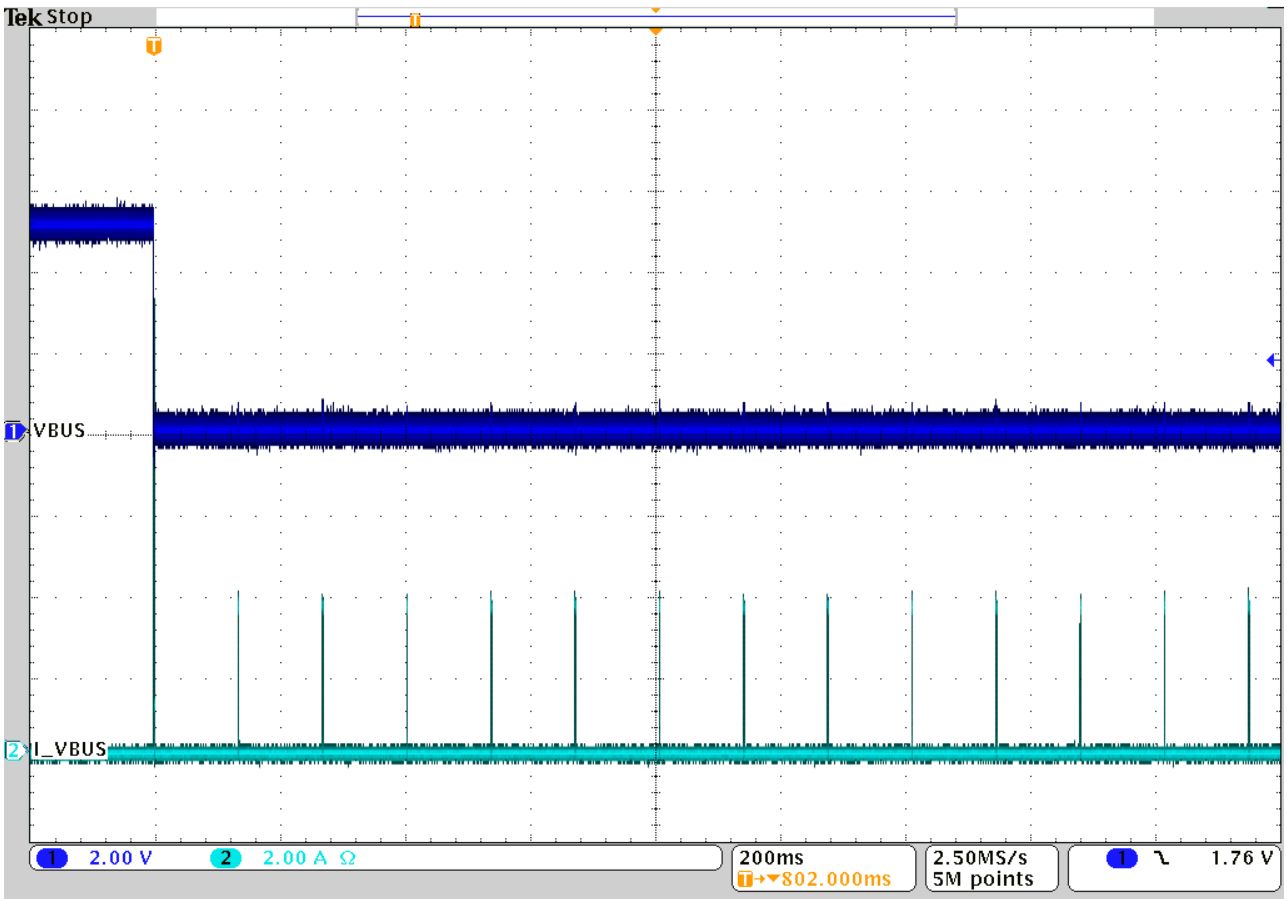

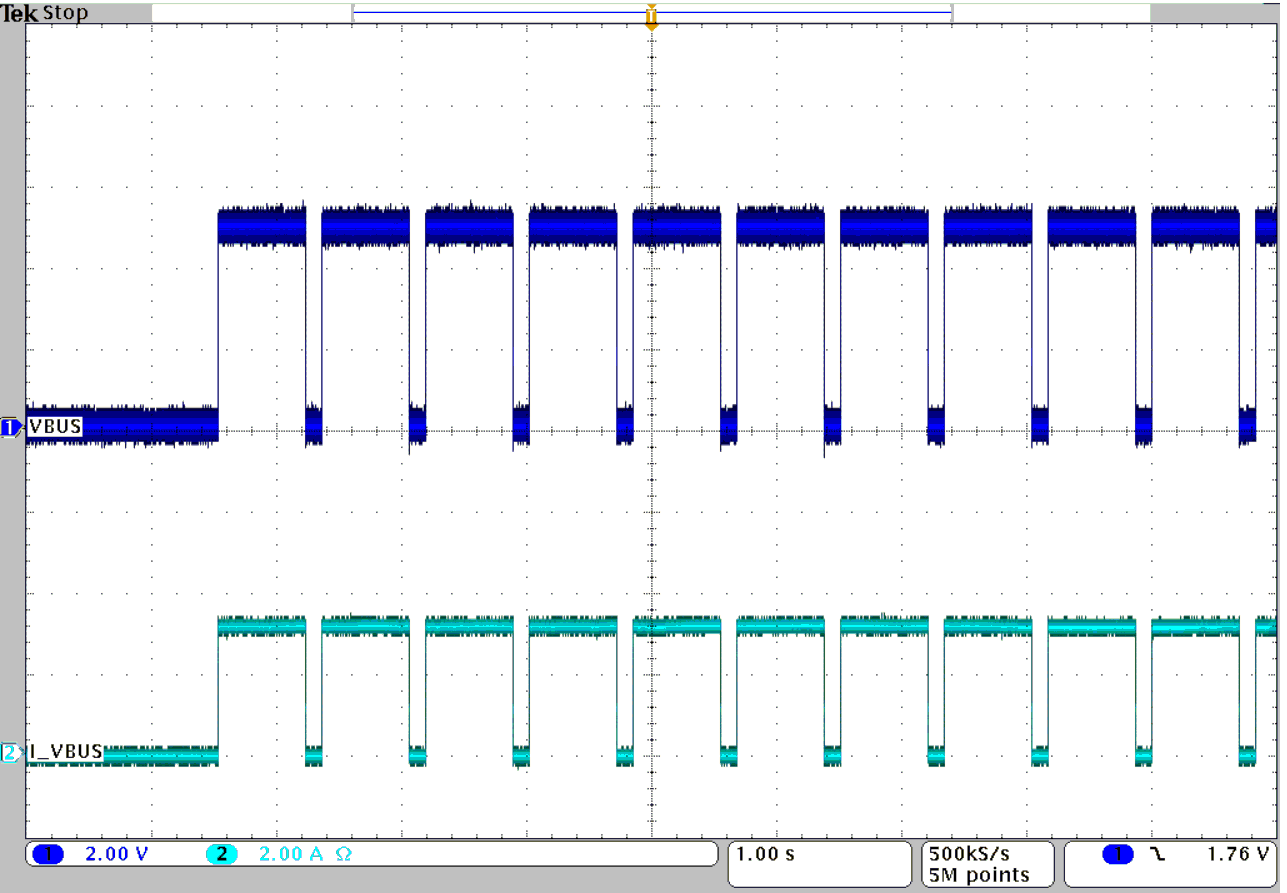

メーカーから過電流時の波形を入手しましたので添付致します。

負荷1.25Ω時の波形

ご確認お願い致します。

以上、宜しくお願い致します。 -

投稿者投稿

電源IC

電源IC