ホーム › フォーラム › Texas Instruments › その他 › DRA829のOFFシーケンスについて

このトピックには5件の返信が含まれ、2人の参加者がいます。2 年、 11 ヶ月前に guest さんが最後の更新を行いました。

-

投稿者投稿

-

guestDRA829のOFFシーケンスについて

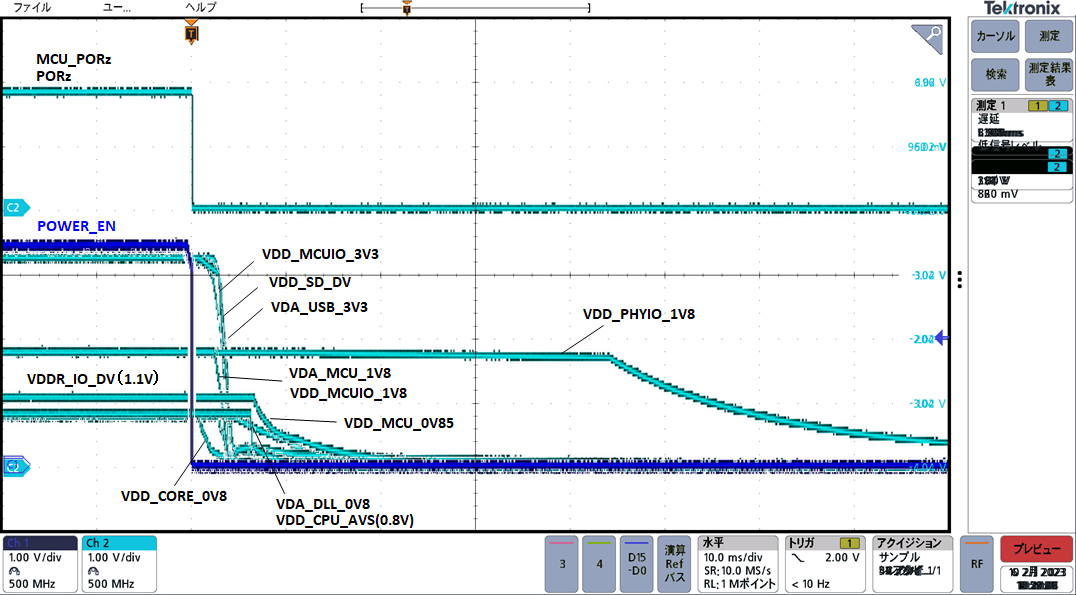

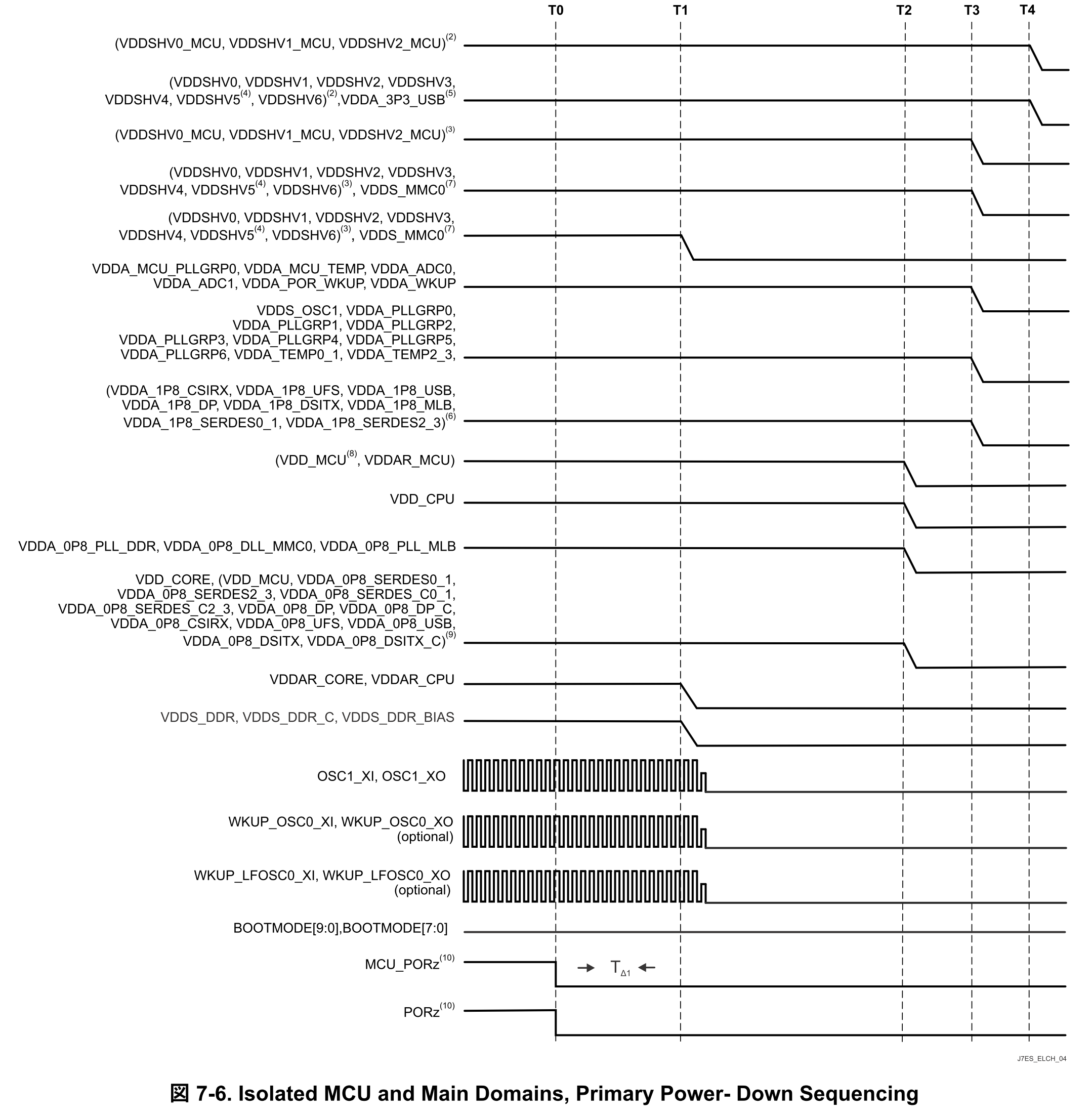

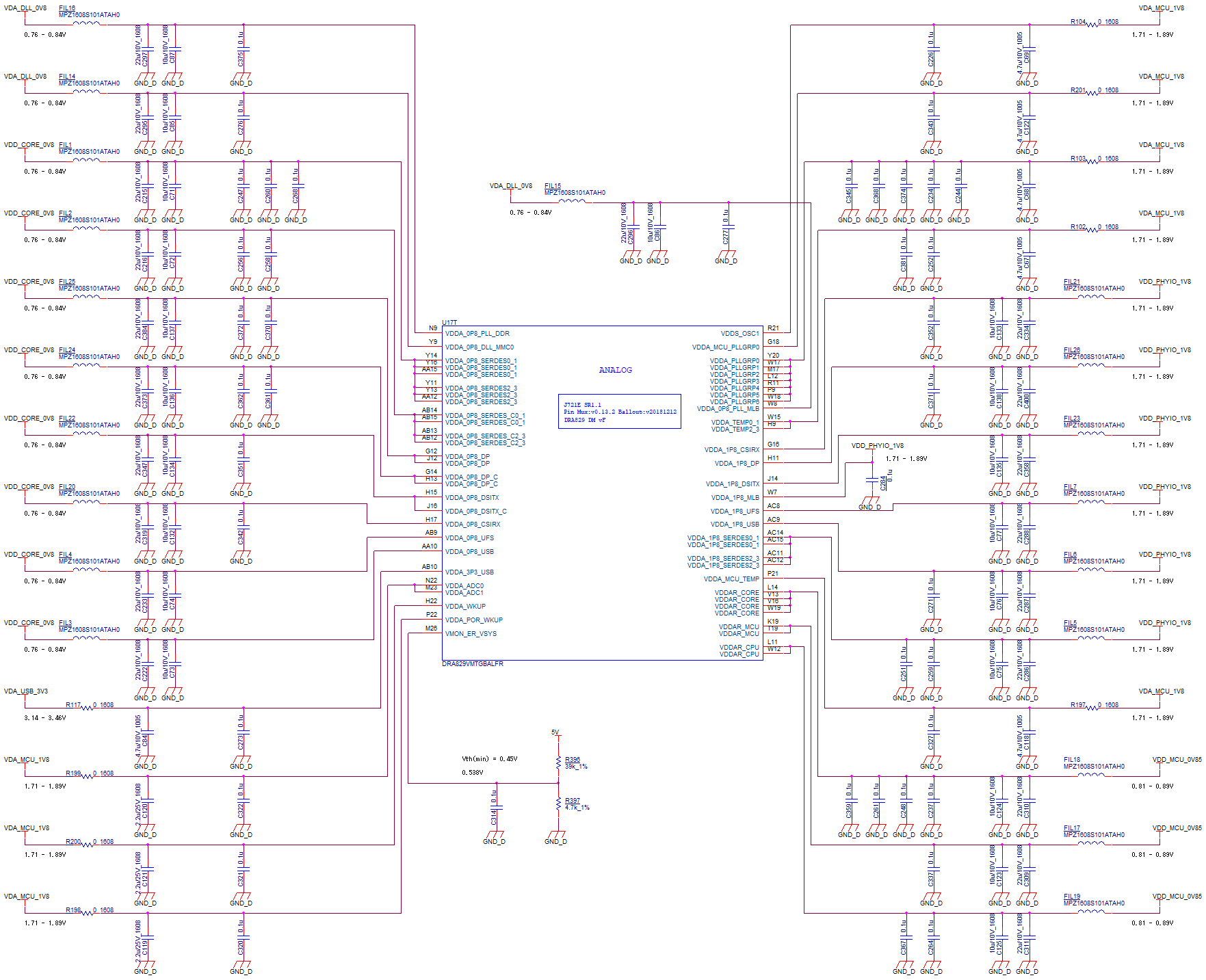

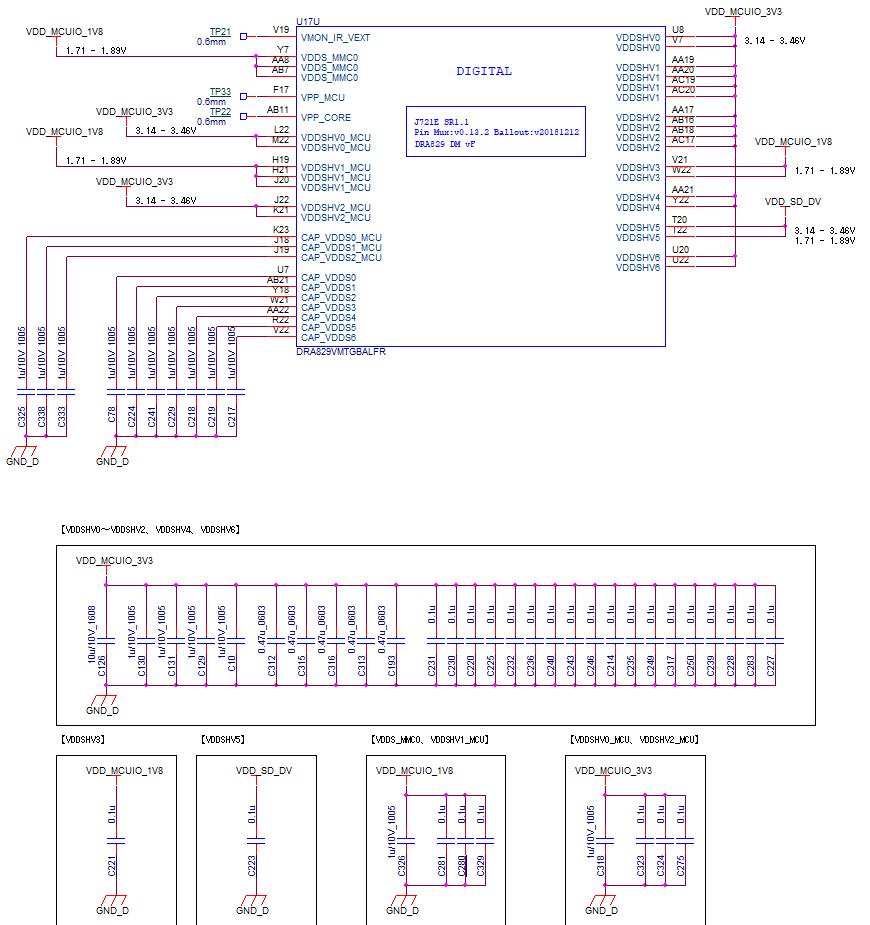

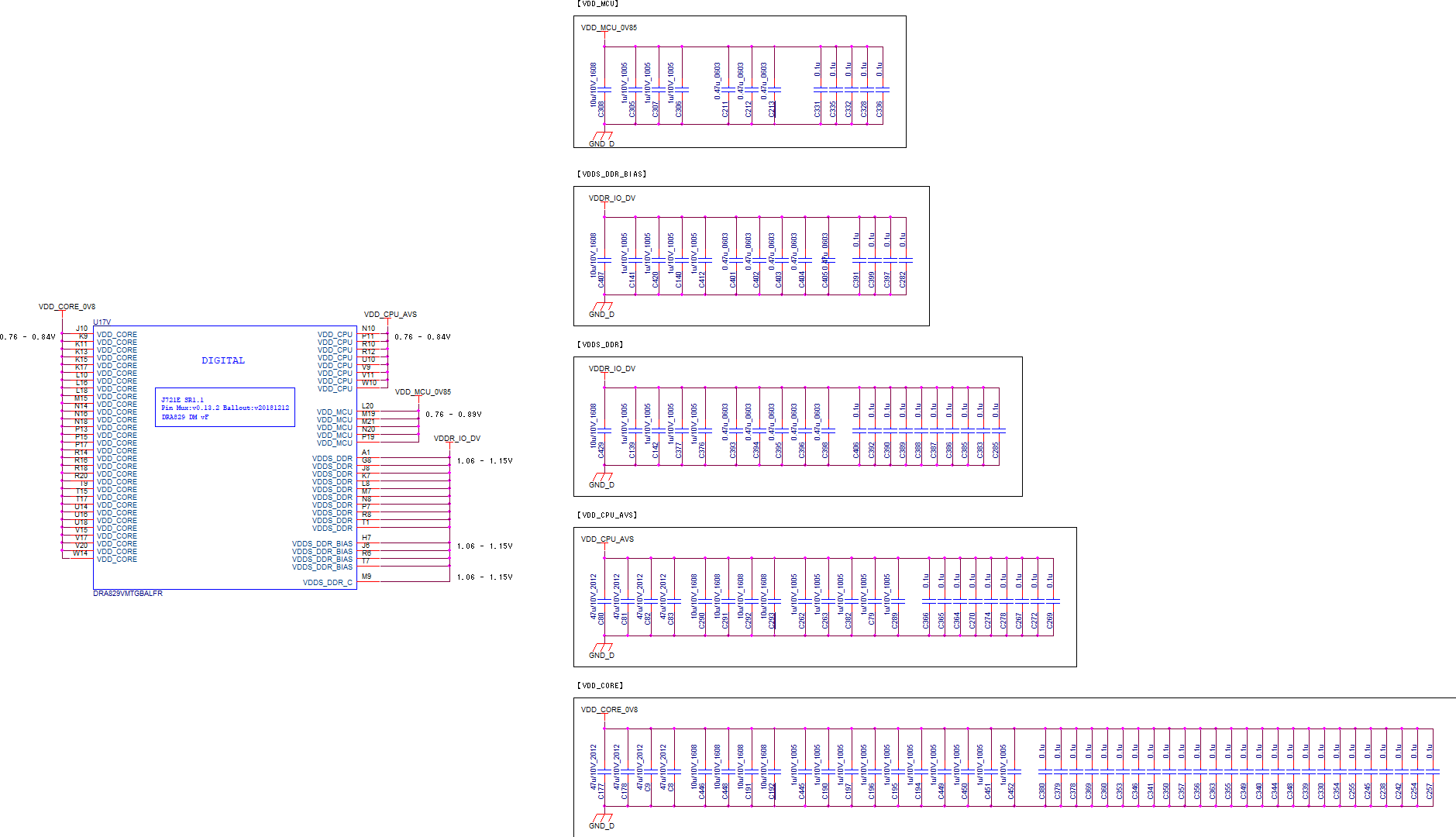

<p style=”text-align: left;”>DRA829のOFFシーケンスについて、メーカーの推奨に違反した場合にどのような懸念点があるかメーカー様にご確認頂けないでしょうか。現在、弊社で設計を行った基板にて、DRA829のOFFシーケンスがデータシートのセクション 7.10.2.5 に記載されているOFFシーケンスを守れていない状況です。PMICは使用しておらず、電源はDCDCまたはLDOで生成しております。以下にOFFシーケンス波形、データシートの推奨、DRA829の電源回路を添付いたします。特にVDDA_1P8_***で使用しているVDD_PHYIO_1V8が他の電源より遅れており、DRA829に損傷を与える可能性がないか危惧しております。</p>

お問い合わせありがとうございます。

頂いたご質問についてはメーカーに確認させていただきますので、大変恐縮ですが少々お時間頂けますと幸いです。

なお、返答内容によっては、直接メールにてご連絡させて頂きますが、予めご容赦ください。

以上、よろしくお願いいたします。

guest上記進展があればご連絡頂けると助かります。

本件、ご連絡が出来ておらず大変申し訳ございません。

現時点でメーカーより回答がいただけておらず、何度か催促している状況となります。回答が有り次第ご連絡させて頂ければと存じますので、大変恐縮ですが、もう少々お時間頂けますと幸いです。

以上、何卒よろしくお願いいたします。

本件、ご回答が遅くなり大変申し訳ございません。

メーカーへ確認させて頂いた結果、TI 社としては、推奨されるパワーダウンシーケンスに違反した場合の特定の故障メカニズムについて認識しておらず、回答出来かねるとのことです。最も安全な推奨事項は、SOC電源のアップ/ダウンシーケンスが満たされるようにPCB設計を変更するとのことです。

また、すべての J7 デバイスは、「突然の電源断」時のパワーダウンについて、以下の重要な推奨事項がありますので、ご確認ください。

- MCU_PORz&SOC_PORzをすぐにアサートして、SOCを既知の安全な状態にします。(ダウンタイムステップあたりJ 7あたり0 ms)

- SRAM (0.85 V) の供給は、COREとCPUの前に無効にする必要があります (0.5 ms)

- DDR IO (1.1 V) の供給は、COREの前に無効にする必要があります (0.5 ms)

以下、メーカー原文

==============

TI is not aware of specific fail mechanisms when violating the recommended power down sequencing. The safest recommendation is to modify the PCB design such that the SOC power up/down sequencing is met.In addition, all J7 devices have the following key recommendations for power down in “abrupt power loss”:

1. Assert MCU_PORz & SOC_PORz immediately to put SOC in a known safe state. (0ms per J7 per down time step)

2. SRAM (0.85V) supplies should be disabled before CORE & CPU. (0.5ms)

3. DDR IO (1.1V) supplies should be disabled before CORE. (0.5ms)

=================以上、何卒よろしくお願いいたします。

guestご回答頂きありがとうございます。

上記の件、弊社で対策を検討いたします。

また確認事項が発生した際にはご対応のほどよろしくお願いいたします。

-

投稿者投稿

その他

その他