ホーム › フォーラム › Texas Instruments › マイコン › C2000 › TZ2割り込みが入らない件に関するご相談

このトピックには5件の返信が含まれ、2人の参加者がいます。6 年、 9 ヶ月前に amatsu1 さんが最後の更新を行いました。

-

投稿者投稿

-

TZ2割り込みが入らない件に関するご相談

いつも大変お世話になっております。

現在、TMS320F28027にてテクニカルリファレンスマニュアルを拝読しながら、TZ2端子にHigh→Lowをトリガとして、EPWM3AのA出力をパルスバイパルスでLowとする処理を考えています。

しかし、以下のコードで割り込み及びEPWM3AのA出力がLowになりません。

お手数ですが、原因についてご教示願います。

なお、デバックはTBCLKを動かしながら実施しております。init(){

GpioCtrlRegs.GPAMUX2.bit.GPIO16=0;

GpioCtrlRegs.GPADIR.bit.GPIO16=0;

EALLOW;

//TZ割り込み設定 ch3

Pwm3Regs.DCTRIPSEL.bit.DCALCOMPSEL=0b0001;

EPwm3Regs.TZDCSEL.bit.DCAEVT2=0b011;

EPwm3Regs.TZCTL.bit.DCAEVT2=0b10; // EVT2発生時にEPwm3AをLowレベルとする。

EPwm3Regs.TZEINT.bit.CBC=1; // EVT2発生時にTZEINT割り込みをイネーブルにする。

EPwm3Regs.TZEINT.bit.DCAEVT2=1;

EPwm3Regs.TZSEL.bit.DCAEVT2=1; // EVT2のパルスバイパルストリップをEPwm3_TZINのイベントソース

EPwm3Regs.DCFCTL.bit.PULSESEL=0b01; // 周期の最初でマスク開始

EPwm3Regs.DCACTL.bit.EVT2SRCSEL=0; // とりあえずフィルターは使用しない

EPwm3Regs.TZFLG.bit.DCAEVT2=0;PieCtrlRegs.PIEIER2.bit.INTx3=1; // PIEペリフェラルレベルのイネーブル設定 EPwm3_TZINTはINT2.3

EPwm3Regs.TZSEL.bit.OSHT4=1; // TZ4発生時に1ショットでトリップ

EPwm3Regs.TZSEL.bit.OSHT5=1; // TZ5発生時に1ショットでトリップ

EPwm3Regs.TZSEL.bit.OSHT6=1; // TZ6発生時に1ショットでトリップ

IER|=M_INT2;

EDIS;

}// INT2.3

interrupt void EPWM3_TZINT_ISR(void) // EPWM-3

{

EPwm3Regs.TZCLR.bit.DCAEVT2=1; // DCAEVT2の状態をクリア(TRM P253)

PieCtrlRegs.PIEACK.all|=PIEACK_GROUP2; // PIEグループ2のPIE→CPUへの通知を許可}

-

このトピックは

amatsu1が6 年、 9 ヶ月前に変更しました。

amatsu1さん

TZ2信号の入力設定において、GPAMUX2.bit.GPIO16 に00bを設定されているため、TZ2信号として認識されません。GPAMUX2.bit.GPIO16 = 3; として頂く必要があります。

他のDigital Compare/Trip Zone/割込みの設定については、問題がないように見受けられます。

GPIO設定をご確認いただけますでしょうか。

ご確認のほど、よろしくお願いいたします。

いつも大変お世話になっております。

早急なご対応、誠にありがとうございます。

GPAMUX2.bit.GPIO16 = 3; としたところ、TZ2割り込みに入るようになりました。

ありがとうございました。ただし、以下の問題が解消されませんでした。

①TZ2がHighからLowになった時にPWM出力がHighのままで次の周期でPWM出力が丸々Lowとなる

②TZ2がHighからLowになった時にTZ2割り込みが毎回入らず、稀に入った時もHighからLowになってから7usの遅延の後、割り込みが入る以上、ご対応何卒宜しくお願い致します。

-

この返信は6 年、 9 ヶ月前に

amatsu1 さんが編集しました。

いつも大変お世話になっております。

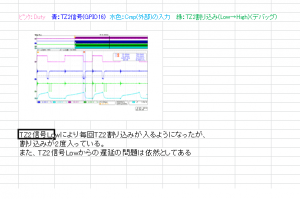

その後こちらでも原因解析した結果、以下の通り状況が変わりましたので、ご連絡致します。①TZ2がHighからLowになった時にPWM出力がHighのままで次の周期でPWM出力が丸々Lowとなる

→自己解決致しました。

(EPwm3Regs.TZCTL.bit.TZA=0b10;を加えたところ、TZ2がHighからLow時にPWMがHighからLowになりました。)②TZ2がHighからLowになった時にTZ2割り込みが毎回入らず、稀に入った時もHighからLowになってから7usの遅延の後、割り込みが入る

→TZ割り込みが入ったことを確認するための目印が違っていました。大変申し訳ございません。

目印を直して、割り込みクリアレジスタを見直したところ、TZ2がHighからLowになった時に毎回TZ2割り込みが入るようになりました。しかし、以下の問題が残っております。③割り込みが2回入ってしまう。

④割り込み発生までに遅延がある。なお、最新のコードは以下の通りとなります。

TZ_init(){

GpioCtrlRegs.GPAMUX2.bit.GPIO16=3;

GpioCtrlRegs.GPADIR.bit.GPIO16=0;//TZ割り込み設定 ch3

EPwm3Regs.DCTRIPSEL.bit.DCALCOMPSEL=0b0001;

EPwm3Regs.TZDCSEL.bit.DCAEVT2=0b011;

EPwm3Regs.TZCTL.bit.DCAEVT2=0b10; // EVT2発生時にEPwm3AをLowレベルとする。

EPwm3Regs.TZCTL.bit.TZA=0b10; // EVT2発生時にEPwm3AをLowレベルとする。

EPwm3Regs.TZEINT.bit.CBC=1; // EVT2発生時にTZEINT割り込みをイネーブルにする。

EPwm3Regs.TZSEL.bit.DCAEVT2=1; // EVT2のパルスバイパルストリップをEPwm3_TZINのイベントソースとしてイネーブルにする。

EPwm3Regs.DCFCTL.bit.PULSESEL=0b01; // 周期の最初でマスク開始

EPwm3Regs.DCFOFFSET=0; // マスクのオフセット期間は0

EPwm3Regs.DCFWINDOW=15; // 600:10us = x:240ns(マスク期間)より、 x = 14.4 ≒ 15

EPwm3Regs.TZCLR.bit.DCAEVT2=1;

EPwm3Regs.TZCLR.bit.CBC=1; // DCAEVT2の状態をクリア(TRM P253)

EPwm3Regs.DCACTL.bit.EVT2SRCSEL=0; // とりあえずフィルターは使用しない

EPwm3Regs.TZFLG.bit.DCAEVT2=0;

PieCtrlRegs.PIEIER2.bit.INTx3=1; // PIEペリフェラルレベルのイネーブル設定 EPwm3_TZINTはINT2.3

}

// INT2.3

interrupt void EPWM3_TZINT_ISR(void) // EPWM-3

{

DINT; //グローバル割り込み禁止

EALLOW; //書き込み保護解除

EPwm3Regs.TZCLR.all=0x007F;

PieCtrlRegs.PIEACK.all|=PIEACK_GROUP2; // PIEグループ2のPIE→CPUへの通知を許可

//デバッグコード

GpioDataRegs.GPACLEAR.bit.GPIO18=1;

GpioDataRegs.GPASET.bit.GPIO18=1;

//ここまでデバッグコード

IER|=M_INT2;

EDIS; //書き込み保護設定

EINT; //グローバル割り込み許可

}また、具体的な波形は添付の通りとなります。

大変恐縮ではございますが、ご対応何卒宜しくお願い致します。

-

この返信は6 年、 9 ヶ月前に

amatsu1 さんが編集しました。

Attachments:

amatsu1さん

③割り込みが2回入ってしまう。

こちらにつきまして、割込みフラグ(TZFLG)をTZCLRレジスタにてクリアしたタイミングにおいて、要因が継続している場合は、再度割り込みフラグがセットされ、割込みが発生いたします。

そのため、Cycle by cycleをご利用の際に1PWM周期内に割込みを複数回発生させたくない場合は、最初のTZ割込みでは、割込みを禁止(TZEINTにて禁止)し、次のPWMのCTR=0のタイミングで許可(TZEINT[CBC]=1)とする必要があります。また、割込み処理の記述を拝見したところ、以下の処理が問題を起こす可能性がございますので、ご確認ください。

- グローバル割込みの禁止/許可設定

割り込みハンドラ実行時は、グローバル割込みは禁止となっており、割込み処理から復帰(リターン)する際に、許可されます。明示的に関数内で許可を行うと、他の割込みが発生する可能性がありますので、DINTおよびEINTは削除いただけますでしょうか。

また、IER=M_INT2;を実行頂いておりますが、IERは割込みの発生により変化いたしませんので、この処理は必要ありません。 - PIEACKレジスタアクセスについて

PieCtrlRegs.PIEACKレジスタにつきましては、1の書き込みで対象ビット(割込み)要求のクリアと、その要因(PIEIFRx)が残っている場合は、CPUへ割り込み要求を行います。提示いただいたコードでは、”|=”にてPIEACKをクリアしていますが、”|=”では他のレベルの割込みに影響いたします。ORではなく、直接代入”=”をご利用ください。

④割り込み発生までに遅延がある。

割込み発生までの遅延につきましては、通常処理において、割込み禁止が行われている可能性がございます。

通常(メイン)ループ処理において、割込み禁止を設定されていないか、ご確認いただけますでしょうか。また、HRPWMをご利用の場合、SFO関数で使用しているランタイムライブラリの影響で、長期間の割込み禁止区間が発生する場合があります。(最大32サイクル≒540usec)

SFO関数については、常に実行する必要はありませんが、いつ長期間の割込み禁止となるかわからない状態では、リアルタイム制御として設計が難しくなるものと思います。そこで、ラインタイムライブラリを修正することで、割込み禁止区間を回避する方法がございます。

詳細につきましては、添付ファイルをご参照いただき、対応いただければと思います。ご確認のほど、よろしくお願いいたします。

Attachments:

いつも大変お世話になっております。

>③割り込みが2回入ってしまう。

ご教示いただいた内容を盛り込んだ結果、

割り込みが1回となりました。

ありがとうございました。> ④割り込み発生までに遅延がある。

こちらにつきましては、どうしても対応しなくてはならない事項ではない為、

一旦保留とさせていただき、時間を見つけて確認させていただきます。ご対応、誠にありがとうございました。

以上、宜しくお願い致します。 -

このトピックは

-

投稿者投稿

C2000

C2000