ホーム › フォーラム › Texas Instruments › オペアンプ › 【ご質問】TPA6130A2EVM I2C接続について

このトピックには9件の返信が含まれ、2人の参加者がいます。6 年、 2 ヶ月前に 短絡亭過電流 さんが最後の更新を行いました。

-

投稿者投稿

-

【ご質問】TPA6130A2EVM I2C接続について

デバイス型番:TPA6130A2表題の件につきまして、1点質問させてください。

新機種(ヘッドフォン)設計につき、TPA6130を採用したく、

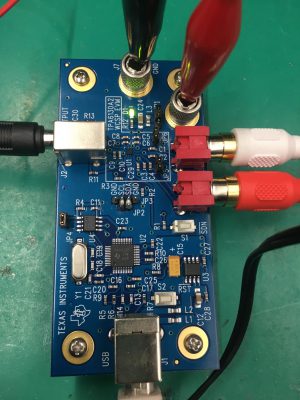

評価ボードを購入して検討させて頂いているのですが、次のような症状がでて評価ができない状況です。USB供給にてアンプに電源供給している状態で、入力へ音源、出力へヘッドフォン接続し、

USB経由でPCへ接続している状態。JP2,JP3はショート状態。

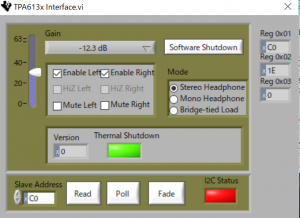

PC側でGUI(TPA613x Interface.vi)を起動し、音源を再生するが、ヘッドフォンから音声が再生されず。

GUI側でGainを調節するが音量変わらず。

画面上では、I2C Statusが赤く表示されており、通信がうまくいっていないことを示している。(添付ファイルforwindows10参照)電源を外部電源に切り替える、PCをWindow10から7の環境で動作させる。ドライバーの再インストール。

等行いましたが結果は同じでした。○評価環境

・PC

Windows10 64bit core i5 (windows7でも同様の症状あり)

ドライバインストールまでは完了しており、デバイスマネージャーには「USB-AudioEVM」

と表示されております。

・GUI

TPA613x Interface.viを上記記述のPCへインストールして使用しています。I2Cの接続不良の原因が分かりません。

ご教授頂けないでしょうか?以上、何卒宜しくお願い致します。

sasuke3567様

御問合せ頂きましてありがとう御座います。

早急にメーカーへ確認致します。回答まで御待ち頂きたく存じます。Polnaref

sasuke3567様

お手数をお掛け致し、申し訳御座いませんが、念の為下記2点について御確認頂けますでしょうか?

1:R2,R3のプルアップ先VDDの電圧

2:レジスタ読み出し時のR2,R3のI2C通信波形御協力頂けます様、宜しく御願い申し上げます。

Polnaref

Polnaref様

インラインにて回答致します。

1:R2,R3のプルアップ先VDDの電圧

A.+5.0V印加されています。オシロスコープで確認済みです。

2:レジスタ読み出し時のR2,R3のI2C通信波形

A.オシロにて確認致しましたが、HighからI2Cの信号が来ている様子がありません。以上、何卒宜しくお願い致します。

sasuke3567

sasuke3567様

御対応頂きましてありがとう御座います。

重ねて御確認頂きたく存じます。

3:C11における[+3.3VD]の有無及び電圧

4:+3.3VDのPower_ON時、及びS2押下直後の、U4_5pin/6pinの波形度々申し訳御座いませんが、御協力頂けます様、宜しく御願い申し上げます。

Polnaref

Polnaref様

以下回答させていただきます。

3:C11における[+3.3VD]の有無及び電圧

A:有、オシロスコープ実測で+3.32V4:+3.3VDのPower_ON時、U4_5pin/6pinの波形

A.Power_ON時→電源投入後、0Vから3.3Vへ立ち上がる

及びS2押下直後の、U4_5pin/6pinの波形

A.添付ファイルを参照お願い致します。以上、何卒宜しくお願い致します。

Polnaref様

上記回答につきまして、

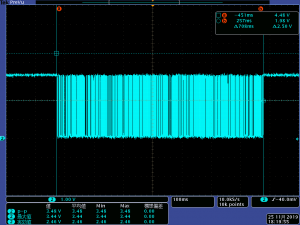

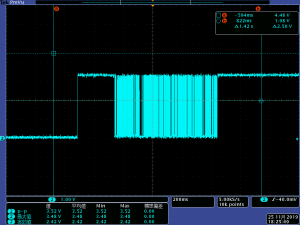

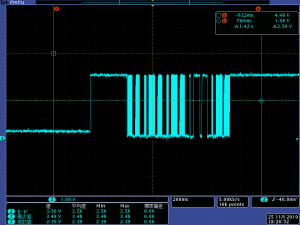

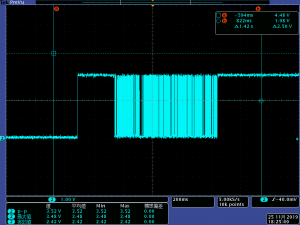

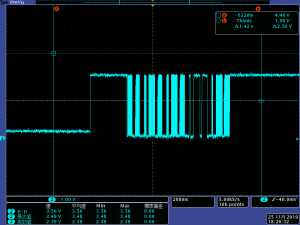

添付画像ファイル名が文字化けしてしまいましたので、改めて添付にて送付させていただきます。4:+3.3VDのPower_ON時、U4_5pin/6pinの波形について

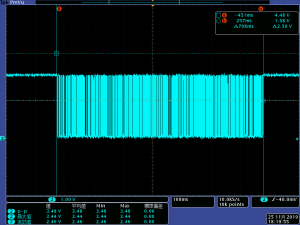

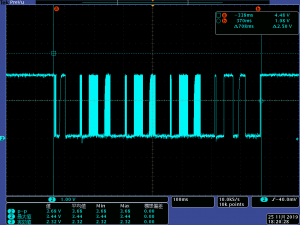

Power_ON 時

U4 5pin 1枚目画像

U4 6pin 2枚目画像

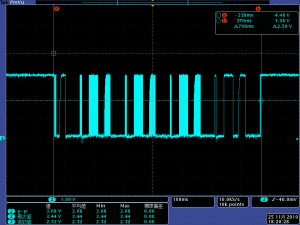

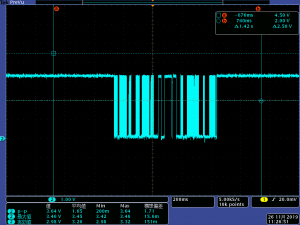

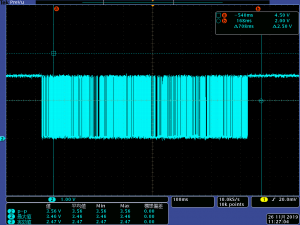

S2スイッチ押下時

U4 5pin 3枚目画像

U4 6pin 4枚目画像以上、何卒宜しくお願い致します。

sasuke3567様

御対応頂きましてありがとう御座います。

U4_5pin/6pinにてI2Cの波形が存在しておりますので、JP2-JP3を経てR2,R3でも同様の波形が観測されると思われます。

JP2-JP3(U4-U1間)の導通が確実か、御確認頂けますでしょうか。御協力の程、宜しく御願い申し上げます。

Polnaref

sasuke3567様

御対応頂きましてありがとう御座います。

起きている現象の全体像が見えてきました。・SCLの波形がクロックの体をなしておりません。アップして頂きました画像は、SCLとSDAで逆になっておりますでしょうか?

・「SDA.png」がクロック波形とした場合、周波数が一定ではない箇所がいくつか見受けられます。クロックが「歯抜け」となっている個所を拡大して頂けますでしょうか?

・可能であれば、波形を撮る際にSCLとSDAを1つの画面で収めて頂けますでしょうか?

・TPA6130A2のSlave addressは7-bitで[110 0000](x60)です。GUIのアドレス欄の[xCO]を[x60]に変更し、再度お試し頂けますでしょうか?宜しく御願い申し上げます。

Polnaref

-

投稿者投稿

オペアンプ

オペアンプ