ホーム › フォーラム › Texas Instruments › 電源IC › LM3478_Vcc入力変動による異常発振

このトピックには7件の返信が含まれ、2人の参加者がいます。6 年、 1 ヶ月前に wdwune さんが最後の更新を行いました。

-

投稿者投稿

-

LM3478_Vcc入力変動による異常発振

デバイス型番:LM3478LM3478の Vcc電圧が 5.5V~13Vの範囲で変動します。

この時、IC内部のLDOによりDR端子出力には7.2Vが出力されると思われますが、

この、LDO回路が動作する/しない の切り替わりのタイミングで異常発振をしてしまって困っています。出力負荷を大きくする (例 24V/0.7A )と発生するような状態です。

原因はわかりますでしょうか?また、対策のとり方をご教授願います。

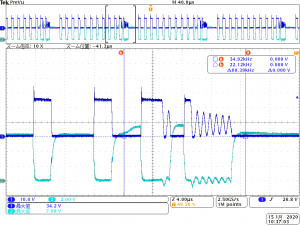

異常発振をしている際の波形のFETのVds/Vgs 波形を添付いたします。

(青:Vds , 水:Vgs)Attachments:

wdwune様

お問い合わせ頂きましてありがとう御座います。

データシートp12、「7.3.1 Overvoltage Protection」の項を御参照頂きたく存じます。御指摘の通りVinから内部Vccを生成して御座いますが、記述の通りVinの変化によるLDOのON/OFF対し、Vfbが振れることが御座います。

おそらくOVPによる停止が働いているものと思われます。

VinにRCフィルタを入れ、Vinの急な変化を抑えることが効果的と存じます。ご参考になれば幸で御座います。

今後とも宜しくお願い申し上げます。Polnaref

Vin端子に R=56Ω, C=0.1uF でCRフィルタを入れました。

しかしながら、抵抗を入れたことにより、異常発振が出やすくなってしまいました。また、抵抗を R= 56Ω , 100Ω , 1kΩ に変化させてみたところ

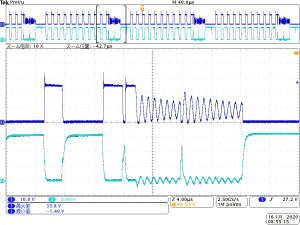

抵抗が大きい方が異常発振が顕著に表れるといった結果でした。Vin端子に R=56Ω, C=0.1uF でCRフィルタを入れた際のVds/Vgsの波形を添付します。

抵抗を入れることで Vgs波形の1パルス内で電圧変動はほぼなくなったのですが、また異なった挙動になりました。

今回の波形の原因もOVPにかかったことによるものなのでしょうか?

また、CRフィルタの抵抗の定数について推奨定数等がありましたら教えてください。Attachments:

情報の追加となります。

Vin 電圧は DC印加で

常に 5.5V ~ 13Vの範囲で変動しているわけではありません。

説明不足ですみません。この内容も踏まえご教授願います。

wdwune様

>> 抵抗を R= 56Ω , 100Ω , 1kΩ に変化させてみたところ

>> 抵抗が大きい方が異常発振が顕著に表れるといった結果でした。

電力用フィルタとしてはRが大きすぎる感じが御座います。データシートのp22、「8.2.1.2.8 Input Capacitor Selection」項にRCフィルタの定数に関する記載が御座いますので、御参照頂きたく存じます。

VinからVccの間にRCにてΠ型フィルタを構成し、その際のRCの定数は、Vin -> 10uF -> 20Ω -> 1uF -> Vccが宜しいかと存じます。今後とも宜しくお願い申し上げます。

Polnaref

ご指摘の通り、抵抗/コンデンサを調整したところ

異常発振を抑えることができました。対策を行っている中で気になった点なのですが

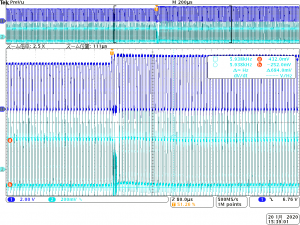

Vin端子の抵抗 R を大きくしすぎると、動作電流を引けなくなる以外にどのような問題が起こるのでしょうか?また、抵抗を 270Ω つけてみたところ、 Vin端子電圧が 添付波形のようになりました。

(添付波形 青:Vgs , 水色:Vin)

Vin端子電圧が、 700mV ~ 800mVのリップル幅を持ってしまいました。

この理由としてはどのようなことがあげられるでしょうか?

ご教授願います。

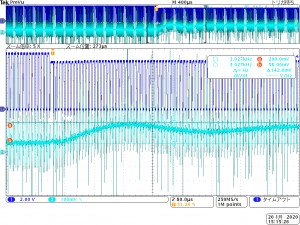

(比較として220Ωを付けた際の波形を2枚目に添付します。)wdwune様

>> 動作電流を引けなくなる以外にどのような問題が起こるのでしょうか?

ICとしましては、データシート記載のVcc(min)を割り込まなければ正常に動作致します。

考えられるのは、設計後の実動作上において、放射ノイズの懸念が考えられます。FETをONする際のGate電圧がVccの変動に依存するため、電圧によってFETのTurn-ON/OFF時間が変化致します。

PWBのパターンが適切であれば”ある程度は”抑えられますが、さらなる対策が必要となりますと、FETのGate抵抗の調整が必要になると思われます。

Gateの抵抗を大きくしますと、放射のレベルは低減しますが、その分FETでのスイッチ損が増加し、その分放熱を要する場合が御座います。つまり、Vccが変動する環境下では、放射ノイズに対する対策の「最適点」を見つけることが難しくなります。

従いまして、今回のケースでは、もし可能ならばVccの固定(Max6.5V程度でクランプ)が望ましく思います。

Polnaref

ご回答ありがとうございました。

上記内容にて解決いたしました。

-

投稿者投稿

電源IC

電源IC