ホーム › フォーラム › Texas Instruments › 電源IC › TPS40200 評価ボード 部品の用途について

このトピックには10件の返信が含まれ、2人の参加者がいます。5 年、 11 ヶ月前に 短絡亭過電流 さんが最後の更新を行いました。

-

投稿者投稿

-

TPS40200 評価ボード 部品の用途について

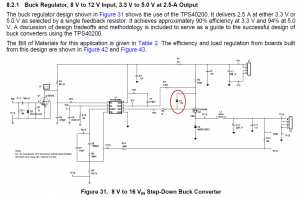

デバイス型番:TPS40200TPS40200評価ボード(TPS40200EVM-001)の

ユーザーズガイド(SLVU147C) p3に記載されております回路図では

TPS40200のDRVpinとQ2のソースの間にD1が接続されておりますが、

D1を用意されている理由は何でしょうか?GDRV端子の保護でしょうか?

Attachments:

maida様

お問い合わせ頂きましてありがとう御座います。

このツェナーはGDRV端子電圧の下がり過ぎを抑止するものです。絶対最大定格では、GDRV端子の電圧[VDD-10V]となって御座いますが、寄生インダクタンスの影響によりリンギングが発生する可能性があり、場合によってはFETのVgssを下回ることも御座います。

Vz=12Vのツェナーですので、保護対象はFETのVgssであることが読み取れます。またVinが急激に変化した場合、GDRV端子の電圧がVinに追従しきれずVgsが12V以上となった場合も、ツェナーにより保護が働きます。

個人的にはツェナーと直列に電流制限用の抵抗を入れるべきと考えます。

御参考になれば幸で御座います。

Polnarefご回答ありがとうございました。

追加で2点質問がございます。

■質問1

TPS40200評価ボード(TPS40200EVM-001)ではTPS40200のGDRVpinとPch-FETのソースとの間に

ツェナーダイオードを用意しておりますが、TPS40200のデータしーとの参考回路図では

用意されておりません。

ツェナーダイオードを用意する/用意しないは、何で判断すればよろしいでしょうか?教えて下さい。

■質問2

ツェナーダイオードの用途について下記の回答を頂きましたが、GDRV端子電圧の

実際の許容値を教えて頂けないでしょうか?(VIN +0.3V程度でもOKでしょうか?)

>またVinが急激に変化した場合、GDRV端子の電圧がVinに追従しきれずVgsが12V以上となった場合も、

>ツェナーにより保護が働きます。maida様

■回答1

Vinが頻繁に変化し、且つVinの最大値がFETのVgs_max(ディレーション含む)以上になる場合には、ツェナークランプがあったほうが良いかもしれません。

■回答2

絶対最大定格にてVinと規定されているため、Vinを超える電圧の印加は許容いたしかねます。御了承頂きたく存じます。御参考になれば幸で御座います。

Polnarefご回答ありがとうございました。

こちらで設計しました、TPS40200を使用したVIN24V,VOUT12V回路で

Iout0Aのとき、コイルは電流不連続モードで動作していてGDRV端子には

最大24.3Vの電圧がかかり、VINの24Vを越える電圧が印加しております。

GDRV端子にはVinを超える電圧の印加は許容いたしかねると連絡頂きましたが

0.2~0.3V越えてもIC破損の原因になりますでしょうか?maida様

>> 0.2~0.3V越えてもIC破損の原因になりますでしょうか?

故障原因となります。

如何なる条件であっても絶対最大定格超えている場合には許容いたしかねますこと、御了承頂きたく存じます。Polnaref

ご回答ありがとうございました。

こちらで設計した回路で、Cissの異なる3種類のFETを使用し、出力電流が0Aの場合の

Vgsを確認ました。

FDD4141を使用した場合、データシートに記載されておりますGate driver output voltageのmin値 6Vを下回り、

STD10P6F6を使用した場合、定格の10Vを越えてしましました。

Gate driver output voltageがデータシートで記載されている6~10Vの範囲外で使用した場合

IC故障の原因になりますでしょうか?

特に、Gate driver output voltageのmin値の6Vより小さい場合、IC故障の原因になりますでしょうか?取得した波形もお送りします。

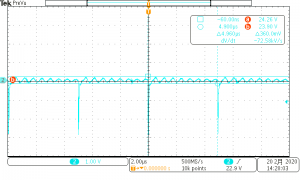

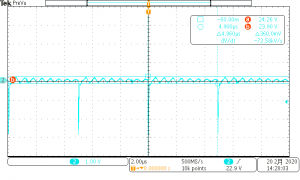

fig1.png FET:FDD4141 (Ciss 2085pF) Vgs 3V (問題点)Gate driver output voltage min値 6Vを下回る。

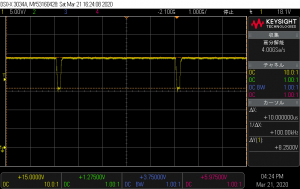

fid2.png FET:FDD5614 (Ciss 759pF) Vgs 8.25V

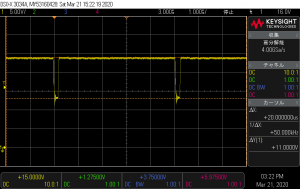

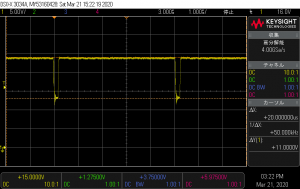

fig3.png FET: STD10P6F6 (Ciss 340pF) Vgs 11.00V (問題点)定格の10Vをover-

この返信は5 年、 11 ヶ月前に

maida さんが編集しました。

maida様

紋切り型の回答で申し訳御座いませんが、GDRV端子の電圧が絶対最大定格を超える条件下におきましては、破損のリスクが御座います。

GDRV-FTE_Gate間に抵抗を入れる等、対策を施してお頂きたく存じます。Polnaref

ご回答ありがとうございました。

絶対最大定格の10Vを越えた場合についてご回答頂きましたが、

fig1のように、Gate driver output voltageがmin値の6Vを下回る使い方をした場合はどうなりますでしょうか?

TPS40200は故障する可能性がございますでしょうか?

fig1.png

(※)FET:FDD4141 (Ciss 2085pF) /Vgs 3Vmaida様

Gate電圧が絶対最大定格を超えない条件下におきましては、Gate電圧が原因となる故障リスクは無いものとお考え頂きたく存じます。

Polnaref

ご回答ありがとうございました。

Ciss 340pFがSTD10P6F6を使用した場合、Vgsが11Vになり定格の10Vを越えてしまいました。(fig3参考)

TPS40200のデータシートに記載されているGate driver output voltageは6~10Vなので、

STD10P6F6を使用した場合もVgsが6~10Vになると思っていたので疑問に感じております。

TPS40200の不具合でしょうか?maida様

TPS40200の本現象につきましては、メーカーサイドから不具合の報告は受けておらず、デバイスの特性に基づくものとなります。

また、本件につきましては、改めて弊社担当よりメールにてご連絡をさせて頂きます。Polnaref

-

投稿者投稿

電源IC

電源IC