ホーム › フォーラム › Texas Instruments › 電源IC › TPS40200のmax電流について

-

投稿者投稿

-

TPS40200のmax電流について

デバイス型番:TPS40200下記URLの機能一覧の表でTPS40200を確認するとIOUT(MAX)が3Aになっておりがなぜでしょうか?

理由を教えて下さい。

外部FETを使用しており、VDDpinとISNSpinとの間に接続するセンス抵抗の定数によりIOUT(MAX)を3Aよりも大きな電流に設定可能であると認識しております。

http://www.tij.co.jp/product/jp/TPS40200?keyMatch=TPS40200DRB&tisearch=Search-JP-everything&usecase=part-numbermaida様

お問い合わせ頂きましてありがとう御座います。

TPS40200はPch-FETドライブの非同期整流DC/DCコントローラです。

既知の通りPch-FETはNch-FETに比べ電子移動度が低くON抵抗が高いため、同じ導通電流でも発熱量はPch-FETが大きくなります。

御指摘の通りFETのパッケージやヒートシンクを含む放熱機構、更には強制空冷を施せばさらに大きな電流を出力することも可能です。しかしながら、TPS40200は過電流検出の閾値(typ100mV)の精度ばらつきが大きく(min55mV/max140mV)、大電流出力には不向きと思われます。

評価ボードにおきましても定格2.5A出力ですが、過電流検出範囲は3.75A~5Aと広くなって御座います。出力段に別途過電流遮断回路を設けるのであれば、大電流電源としてもお使いいただけると思われます。

御参考になれば幸で御座います。

Polnarefご回答ありがとうございました。

FETにはCissやCgのパラメータがございますが、

TPS40200がドライブ可能なFETについて、CissやCgの

max値がございましたら教えて下さい。maida様

FETの使用可否は寄生容量そのものの値ではなく、Vds電圧とTurn_ON/OFF時間、その間に導通する電流の積で現わされる電力損失(FETのスイッチ損)が、FETのTj(ジャンクション温度)上昇に対しどれだけ影響するか、で判断するべきと存じます。

Ronが小さいFETは、QgやCissが大きくTurn_ON/OFF時間が伸びる傾向にありますが、fswが低ければスイッチ損は低減するため、発熱も抑えられます。

fswが高くスイッチ損が大きくとも、シートシンクや強制空冷等の放熱機構があればTjの上昇は抑えられます。紋切り型の回答で恐縮ですが、使用環境や周辺回路、設計/設定等を考慮の上、御判断いただきたく存じます。

Polnaref

ご回答ありがとうございました。

FET使用可否は、電力損失がFETのTj上昇に対しどれだけ影響するかで判断すべきと

連絡いただきましたが、Cissが評価基板に搭載されているFDC654Pの300pFより

たたえば10倍以上の大きなFETを使用すると、TPS40200のDRVpinからの

出力信号をドライブする回路が破損しませんでしょうか?maida様

御指摘の通り破損する可能性が御座います。そのため、寄生容量の大きなFETを使用する際にはFETのGateに抵抗を入れ、Gate電流を制限する必要が御座います。

副作用としまして、スイッチング時のVdsの傾斜が顕著になるため、スイッチ損が増大致します。その結果FETがどれだけ発熱するのか、放熱はどのように行うのか、等ご検討頂きたく存じます。Polnaref

ご回答ありがとうございました。

TPS40200のPch-FETドライバ回路を破損しないようにするために、

FETのCissに対して用意するGate抵抗の抵抗値に指針でもございましたら

教えてください。maida様

Gate抵抗に関しまして、具体的な抵抗値の指針は御座いませんが、電流値の目安はデータシートp5[Gate Driver]に記載の値が参考にできます。

Gate_Drive回路は125mA(min)の電流ソース能力とと200mA(min)の電流シンク能力を有しており、この電流値を上回るとGate電圧(8Vtyp)が低下、FETのスイッチング速度が致します。

Gate電圧の最小値は6Vなので、それぞれ電流値で割りますと、Gate抵抗は

6V/125mA=48Ω

6V/200mA=30Ω

となります。

実基板上では他の寄生成分/抵抗成分もありますので、付加するGate抵抗はさらに小さい値でも問題無い場合が多いです。御参考になれば幸で御座います。

Polnarefご回答ありがとうございました。

1点確認させてください。

データシート figure31,figure44ではDRVpinとFETのゲートは0Ωで接続しており、

データシート figure47はDRVpinとFETのゲートを直結しております。

教えて頂いた抵抗値(30~48Ω)より、ゲート抵抗が小さいようですが

データシート figure31,figure44,figure47の接続では、TPS40200のDRVpinを

駆動する回路が破損する恐れがありますでしょうか?maida様

平均電流でディレーション可能です。例えば10Vin,5VoutならDutyは50%なので1回のスイッチングで流せる電流のピークは倍になります。

Gate抵抗0Ωの場合、理論上Drive電流は瞬間的には無限大となりますが、実際にはFETのGateに寄生抵抗があり、またQgが小さければ電流はその容量を満たす一瞬しか流れないため、平均電流は僅かです。

上記のGate抵抗の考え方は、・Qgが非常に大きいFETで・fswが低く・Dutyが広い(Vin-Vout間電圧差が小さい) 設計に適用されます。

つまりどのようなFETを使用し、入出力条件とスイッチング周波数により、Gate抵抗の有無は変わります。Fig31の設計について考察してみました。

Vin:8V

Vout:3.3V

Iout:2.5A -> Duty=41.25%

fsw:297.6kHz -> Tcycle=3.36usec Ton=1.39usec Toff=1.97usec

FET:FDC654P Rg=6Ω Qg=9nC(Vgs=10V)

FETのTurn-Off_Delayが20nsec(max)で、Qgに9nCの電荷を蓄えるとVgsが-10V(On)から0V(Off)になりますので、Gate_Drive回路に必要な電流供給能力Igateは

Igate=Qg/Toff=9nC/1.97usecc=4.57mA

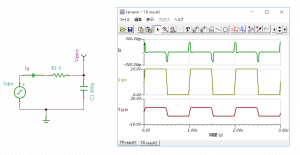

4.57mAですので、TPS40200で十分に補えるため、またFET自体に6Ω程度の抵抗があるため、外付けGate抵抗は基本的に不要と思われます。参考として900pFの容量と6Ωの抵抗で構成されたRCフィルタに、振幅10V(傾斜20nsec)1MHzの矩形波を入力した際の電流をシミュレーション致しました。添付画像を御参照ください。

電流のパルス幅は約60nsecでピークが230mAです。1MHzでも平均(引き抜き電流は除く)で11.5mAなので、周波数が1/3であれば平均電流も1/3になりますので、凡そ計算値と合致致します。御参考になれば幸で御座います。

PolnarefAttachments:

-

投稿者投稿

電源IC

電源IC