- 公開日:2022年01月31日

- | 更新日:2024年03月28日

押さえておきたいDRAMの基礎 Part 2: コマンドとシーケンス

- ライター:Takahashi

- メモリー

はじめに

押さえておきたいDRAMの基礎について2回にわたり紹介します。今回はPart 2として、コマンドとシーケンスについてです。Part 1では、読み書きの原理と内部構造について紹介していますので、こちらも合わせてご確認ください。

押さえておきたいDRAMの基礎 Part 1: 読み書きの原理と内部構造

信号の種類

通信方法

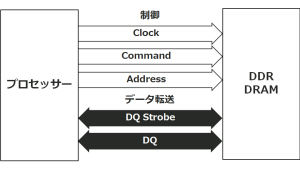

DRAMはクロック同期式のメモリーのため、プロセッサーから送られるクロック信号を基準に動作します。動作を定義するコマンド信号、メモリーセルを指定するアドレス信号は並列に送られ、クロックの立ち上がりエッジに同期します。DDRのデータ転送では、クロックに代わりDQ Strobe(DQS)信号が基準となり、DQバスでデータ転送を行います。コマンド・アドレス信号はクロックの立ち上がりエッジのみに同期するのに対し、データ信号はDQSの立ち上がりエッジ、立ち下がりエッジの両方に同期します。SDRの場合、DQS信号はなく、データはクロックの立ち上がりエッジにのみ同期します。クロックやコマンド・アドレス信号は入力インターフェースのみですが、DQSおよびDQは入出力ができる双方向のバスとなっており、書き込み時は入力、読み込み時は出力で動作します。

図1: DDR DRAMの通信方法

代表的な信号

DRAMの信号の種類は世代によっても異なりますが、代表的なものは以下の通りです。

表1: 代表的な信号

| 信号 | タイプ | 詳細 |

|---|---|---|

| 制御・コマンド信号 | ||

| CLK | Input | Clock: 全ての信号の基準信号。 |

| CKE | Input | Clock Enable: Clockの有効/無効を制御する信号。Highの時、Clockは有効になる。 |

| CS_n | Input | Chip Select: チップの有効/無効を制御する信号。Lowの時、チップは有効になる。 |

| RAS_n, CAS_n, WE_n, ACT_n(1) | Input | Command: High/Lowの組み合わせでコマンドを定義する。 |

| アドレス信号 | ||

| A[17:0](2) | Input | Address: メモリセルを指定する信号。Rowアドレス/Columnアドレス共通の信号だが、タイミングを分けて入力することで別々に指定する。 |

| BA[1:0](2) | Input | Bank Address: Bankアドレスを指定する信号。 |

| BG[1:0](1)(2) | Input | Bank Group: Bankグループを指定する信号。 |

| データ信号 | ||

| DQS | I/O | Data Strobe: DQ信号の基準信号。 |

| DQ[15:0](3) | I/O | Data Input/Output: データ転送を行う信号。 |

(1)DDR4のみの信号

(2)信号数は容量によって異なる

(3)信号数はバス幅によって異なる

電源の種類

電源の仕様は以下の通りです。世代の発展に伴い低電圧化が進んでいます。特徴的なものはVREF電源で、入力信号のHigh/Lowを判定する基準信号としての役割があります。DDR4では、Word線供給電圧であるVPPが追加され、VREFDQが外部供給から内部で生成する仕様に変わりました。

表2: 電源の種類

| 信号 | 詳細 | SDRAM | DDR | DDR2 | DDR3/3L | DDR4 |

|---|---|---|---|---|---|---|

| VDD | 供給電源 | 3.3V | 2.5V | 1.8V | 1.5V/1.35V | 1.2V |

| VDDQ | I/O供給電源 | 3.3V | 2.5V | 1.8V | 1.5V/1.35V | 1.2V |

| VPP | Word線供給電源 | – | – | – | – | 2.5V |

| VREFCA | 制御、コマンド、アドレス信号の リファレンス電圧 | – | VDDQ/2(1) | VDDQ/2 | VDDQ/2 | VDDQ/2 |

| VREFDQ | データのリファレンス電圧 | VDDQ/2 | VDDQ/2 | – |

(1)VREFCAとVREFDQの区別なし

コマンドと状態遷移

代表的なコマンド

DRAMは複数の制御信号とアドレス信号のHigh/Lowの組み合わせでコマンドを定義します。世代を通して基本的なコマンドは同じですが、一部追加コマンドや真理値が異なる場合があります。例えば、DDR4ではACTIVEコマンドを指定する専用信号ACT_nがあるため、ACTIVEコマンドを発行するときは、この信号をLowにし、RAS_n, CAS_n, WE_nはRowアドレスを指定する信号に切り替わります。

表3: 代表的なコマンド

| コマンド | 詳細 | CKE | CS_n | ACT_n(1) | RAS_n | CAS_n | WE_n |

|---|---|---|---|---|---|---|---|

| ACTIVE | Bank/Rowを開き、Read/Writeの準備を行う | H | L | L | L(2) | H(2) | H(2) |

| READ | データの読み込みを行う | H | L | H | H | L | H |

| WRITE | データの書き込みを行う | H | L | H | H | L | L |

| PRECHAGE | Bank/Rowを閉じ、Bit線の電位をVDD/2に戻す | H | L | H | L | H | L |

| REFRESH | セル(コンデンサー)に電荷をチャージする | H | L | H | L | L | H |

| SELF REFRESH | セル(コンデンサー)に電荷をチャージする (Power Down mode時) | L | L | H | L | L | H |

| MODE REGISTER SET | モードレジスターの設定を行う | H | L | H | L | L | L |

(1)DDR4のみの信号

(2)DDR4の場合Row Addressの指定になるため任意の信号

状態遷移

DRAMはIdle状態とActive状態の2つの状態を行き来し、動作しています。Idle状態はトランジスターがOFFでBit線の電位がVDD/2の状態、Active状態はセルを選択するトランジスターがONでセンスアンプによるBit線電位の増幅が完了している状態です。Read/Writeを行うためにはActive状態、Refreshを行うためにはIdle状態である必要があります。これらの原理については、Part 1で説明をしています。

図2: 状態遷移図

① ACTIVEコマンドを発行すると、Bank/Rowアドレスを開きActive状態になる

② Active状態でColunmアドレスを指定し、READ/WRITEコマンドを発行する

③ 一度ActiveになったRowに対しては、再度ACTIVEコマンドを発行せずにRead/Writeを継続することができる

④ Read/Writeの切り替えはActiveなRowであれば直接実行できる

⑤ Idle状態に戻るためには、PRECHARGEコマンドを発行してトランジスターをOFFにすることでRowを閉じ、Bit線の電位をVDD/2に戻す

⑥ 電荷保持に必要なRefreshはIdle状態で行うことができる

⑦ Mode RegisterへのアクセスはIdle状態で行うことができる

シーケンスとタイミング

Read/Writeシーケンス

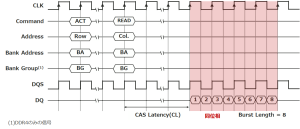

ReadはDRAMからプロセッサーへのデータ転送で、DQSとDQは出力になります。まず、クロックの立ち上がりエッジのタイミングでACITVEコマンドを発行し、同時にRowアドレスを指定します。次に、同じくクロックの立ち上がりエッジのタイミングでREADコマンドを発行し、同時にColumnアドレスを指定します。そして、一定の遅延時間を満たすとデータの出力が開始されます。データはバースト転送され、一回のREADコマンドで複数のデータが転送されます。データ出力の遅延時間はCAS Latency(CL)と言い、動作周波数ごとに設定できるサイクル数が決まっています。なお、Read動作では、データはDQSと同位相で出力され、プロセッサー側でデータを遅延させることでセットアップ/ホールドを確保しています。

図3: Readシーケンス

WriteはプロセッサーからDRAMへのデータ転送で、DQSとDQは入力になります。基本的なシーケンスはREADと同様で、WRITEコマンドを発行する前にACTIVEコマンドを発行する必要があります。データ入力も同様に、一定の遅延時間を満たした後バースト転送されます。Writeの遅延時間はCAS Write Latency(CWL)と言い、一般的にはReadよりWriteの方が遅延時間は短いです。Readとの大きな違いは、DQSとDQの位相が異なることです。Readは同位相でしたが、Writeは1/4位相がずれて入力されます。

図4: Writeシーケンス

アイパターンとセットアップ/ホールド

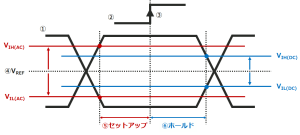

アドレス信号やデータ信号など、High/Lowが激しく遷移する信号は、開いた瞳のように見えることからアイ(Eye)パターンを呼ばれます。信号のラッチにおいては、このアイパターンが大きく開いていることが重要です。信号を正しくラッチするためにはセットアップタイムとホールドタイムを満たす必要があります。セットアップタイムは、クロックなどの基準信号の変化前にラッチする信号を準備させおく最小時間のことで、ホールドタイムは、基準信号の変化後にラッチする信号を保持しておく必要がある最小時間のことです。DDR以降では、セットアップは、VREFを基準にVIH/IL(AC)を通過したタイミングから基準信号の変化エッジまでのタイミング、ホールドは、基準信号の変化エッジからVREFを基準としたVIH/IL(DC)を通過したタイミングとして規定されています。

図5: セットアップ/ホールド

表4: 信号別セットアップ/ホールドの仕様

| ①信号 | ②基準信号 | ③エッジ | ④リファレンス 電圧 | パラメーター | |

|---|---|---|---|---|---|

| ⑤セットアップ タイム | ⑥ホールド タイム | ||||

| コマンド・アドレス | CLK | ↑ | VREFCA | tIS | tIH |

| データ | DQS | ↑↓ | VREFDQ | tDS | tDH |

おわりに

今回はDRAMのコマンドとシーケンスについて紹介しました。Part 1では、仕組みを理解する上で重要な内部構造について紹介していますので、合わせてご確認ください。

押さえておきたいDRAMの基礎 Part 1: 読み書きの原理と内部構造

マクニカ取り扱いメーカー・マイクロン社の最新製品とDRAM製品ラインアップはこちら。

SDRAM,DDR,DDR3,DDR3

LPDDR4/4X SDRAM

DDR5 SDRAM

Micron社のDRAM製品をお探しの方は、以下の製品ページもぜひご覧ください。